1. 기억장치 시스템 개요

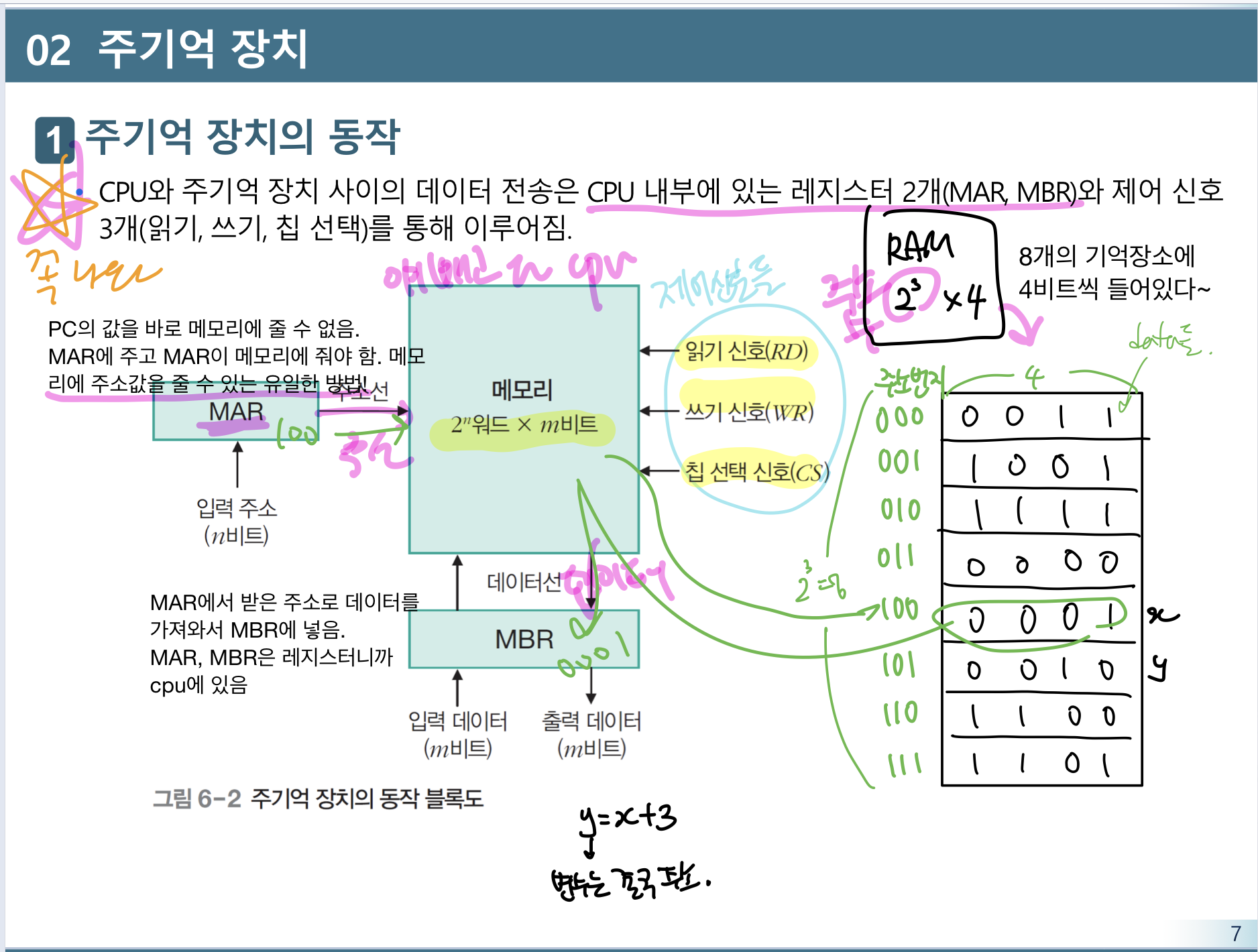

2. 주기억장치

**2KByte = 2 * 2^10 * 8

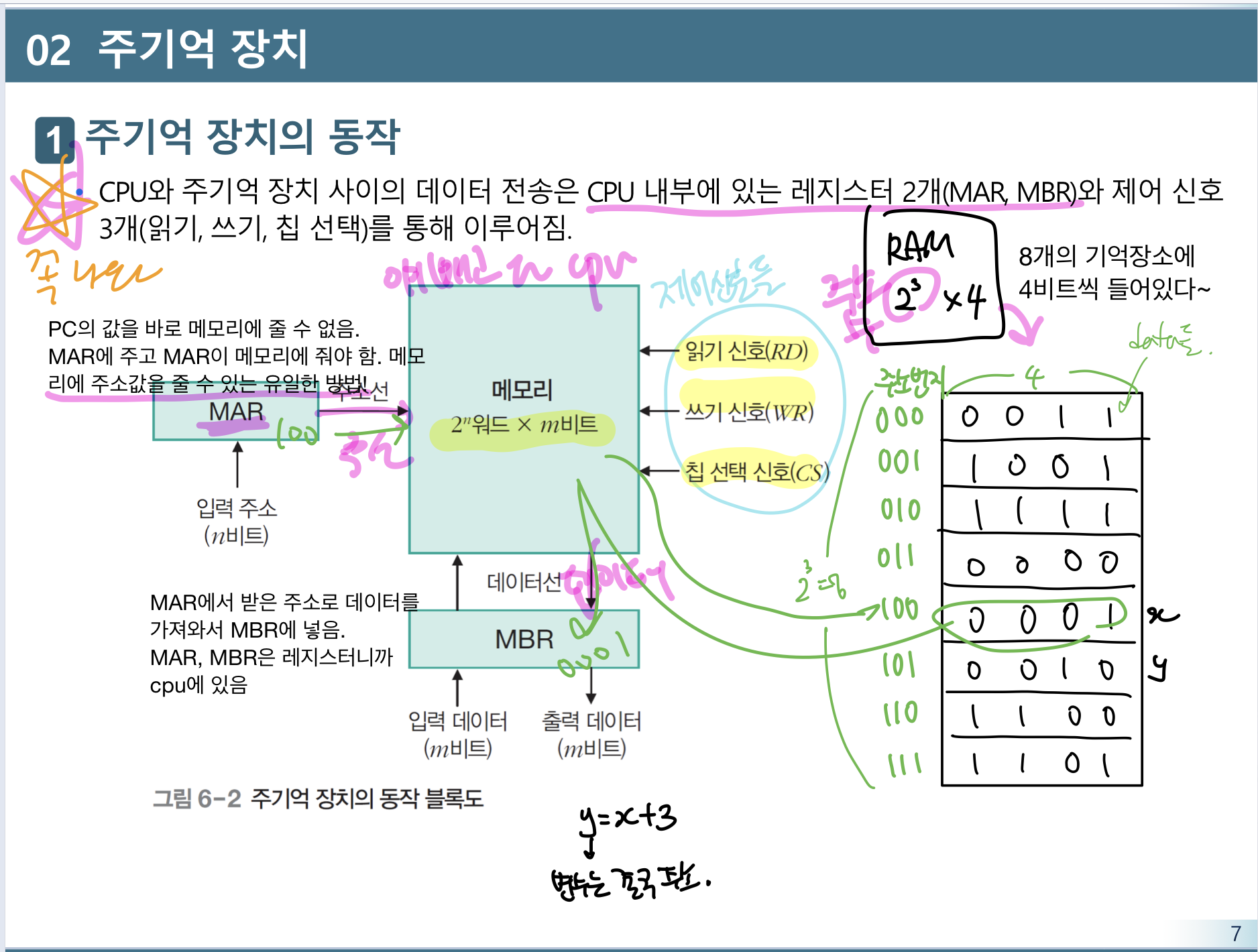

기억장치 용량 = 2^n * m

→ PC, MAR = n비트

MBR = m비트

주소길이 = n비트. 주소개수 = 2^n

ex) 64KByte RAM = 주소비트가 2^6*2^10 → 16개. 데이터 비트가 8 → 8개

리틀엔디안 : 하위 자리수(바이트)를 낮은 주소에

- ROM(비휘발성. 영구) - 조합회로. 펌웨어저장. 주메모리의 일부 구성

- 마스크 ROM : 제조 시 영구

- PROM : programmable 사용자가 한번 씀. 변경불가

- EPROM : eraseable 자외선으로 복원 가능

- EEPROM : electrically 전기신호로 복원 가능. 플래시메모리(usb.비휘발성 RAM과 입출력가능ROM 장점 동시. 재사용 횟수 제한.)

- RAM(위치관계없이 시간 동일. 휘발성)

- SRAM : 플립플롭. 집적도는 낮으나 비싸고 빠르고 전력많이 먹지만 재충전 필요없어 캐시에 쓰임

- DRAM : 커패시터에 전하 충전. 주기억장치mm

** 위에 바가 있으면 0일 때 동작. CS는 칩 선택 신호. CS와 R/W에 모두 동작신호가 들어와야 동작.

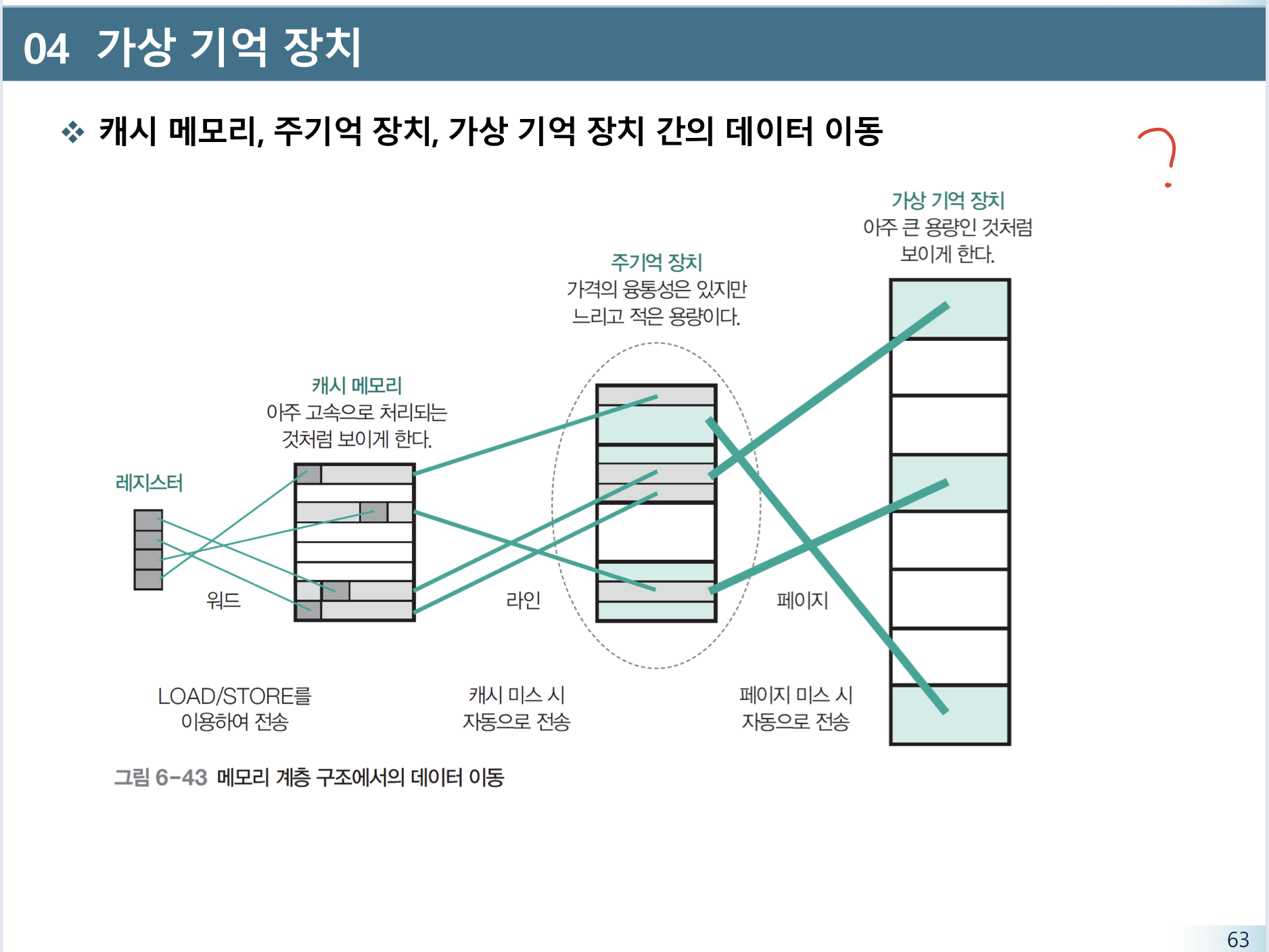

3. 캐시기억장치

캐시 히트율 H

평균 기억장치 액세스 시간 : HTc + (1-H)Tm

참조 지역성

- 공간적 지역성 : 인접

- 시간적 지역성 : 최근 액세스 가까운 미래에 다시 액세스

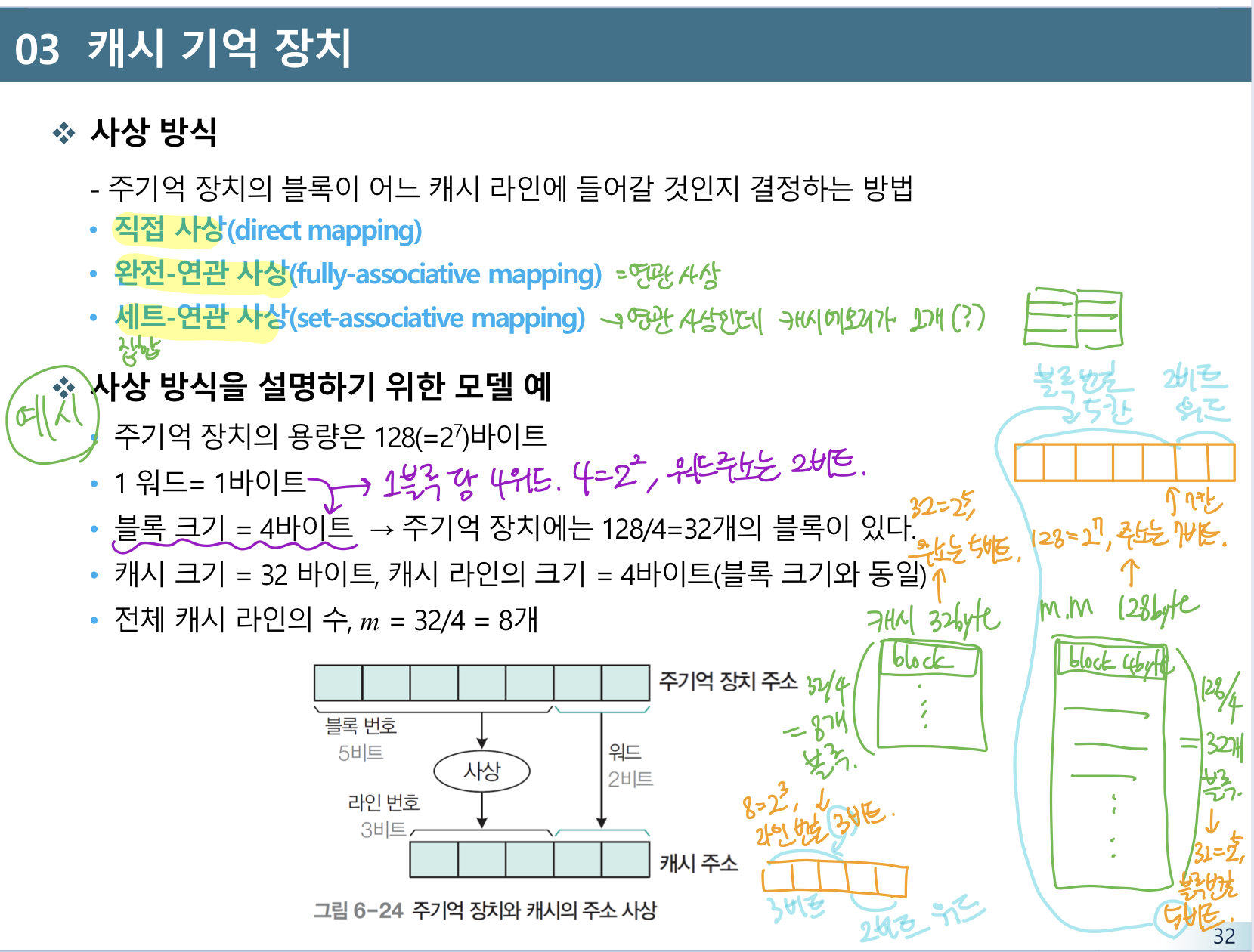

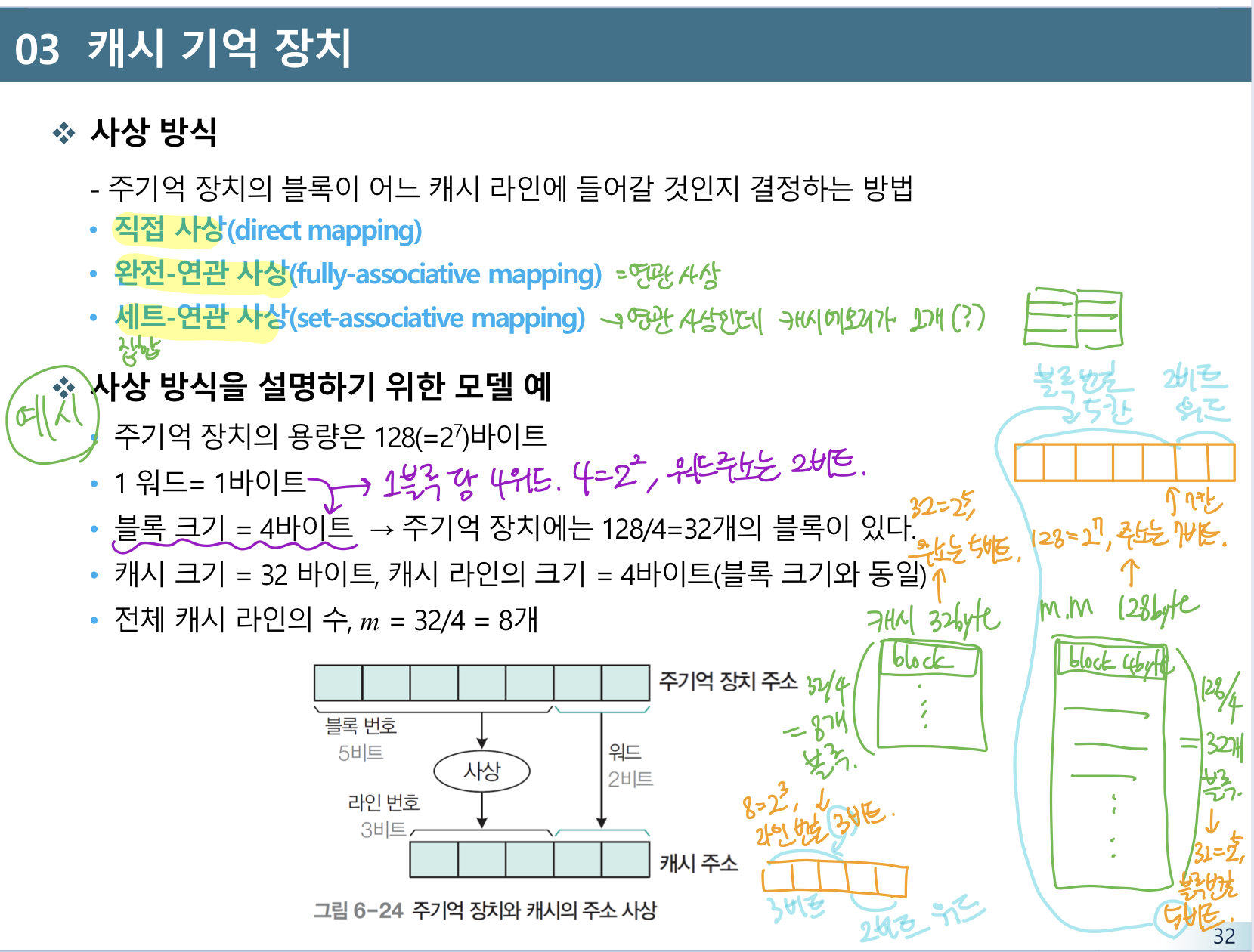

사상 방식(mapping scheme)

블록은 k개의 워드로 구성. 주기억장치 -블록mapping됨- 캐시 -워드- cpu

캐시가 블록을 갖다놓는데 블록하나가 들어가는 공간이 라인(=frame). 그래서 라인도 k개의 워드로 구성.

tag는 라인에 적재되어있는 블록 구분 정보.

주소는 tag + line + word 구분영역으로 구성(연관사상은line없음)

직접 사상 : 주기억장치의 블록번호에서 앞부분 비트를 태그로 사용하고 뒷부분 비트로 캐시의 어느 라인(frmae)으로 갈 지 직접 정해져 있음. cd, hdd

간단. 비용적음. 같은 라인에 들어갈 블록을 반복적으로 사용하면 히트율 떨어짐

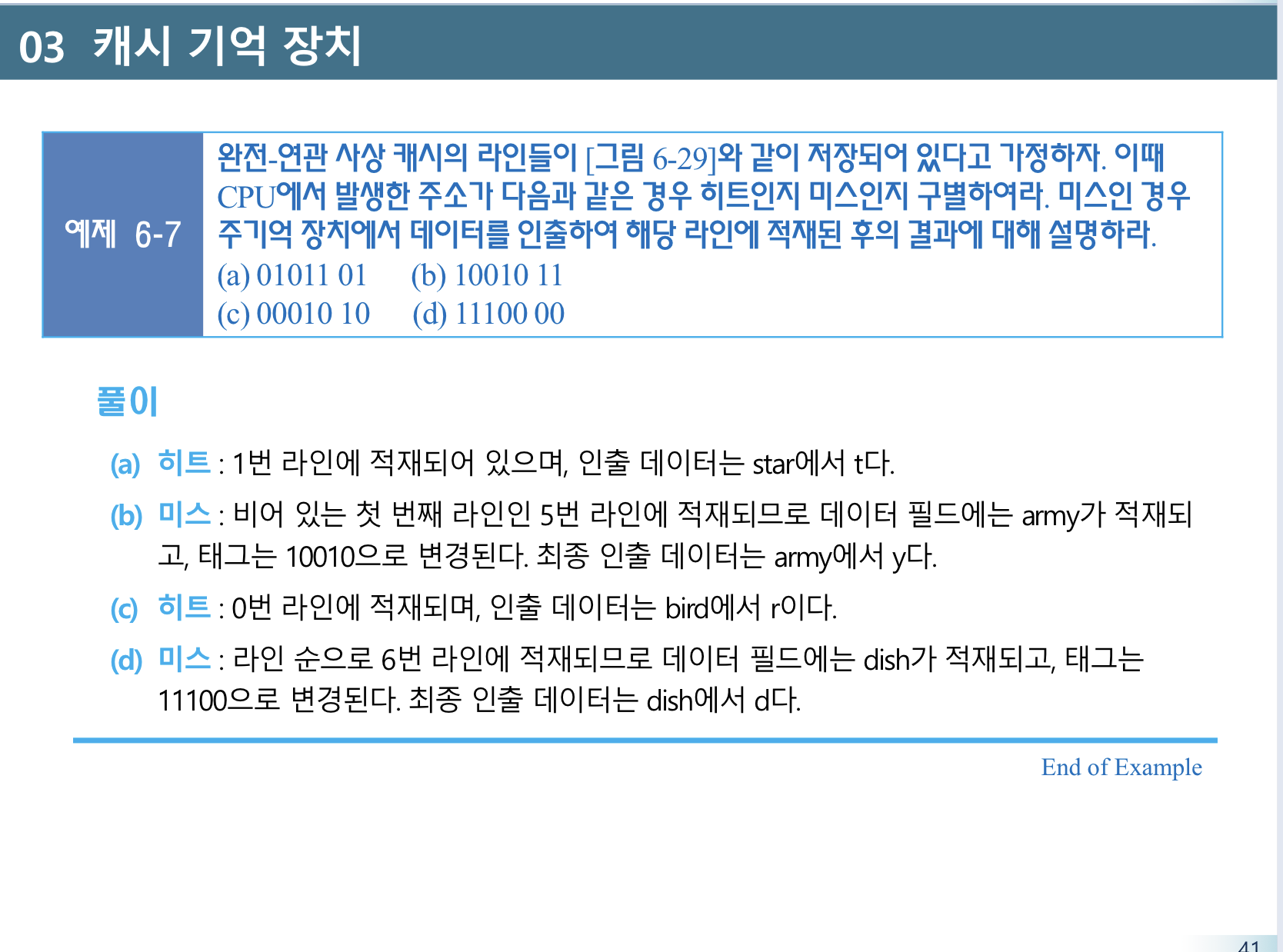

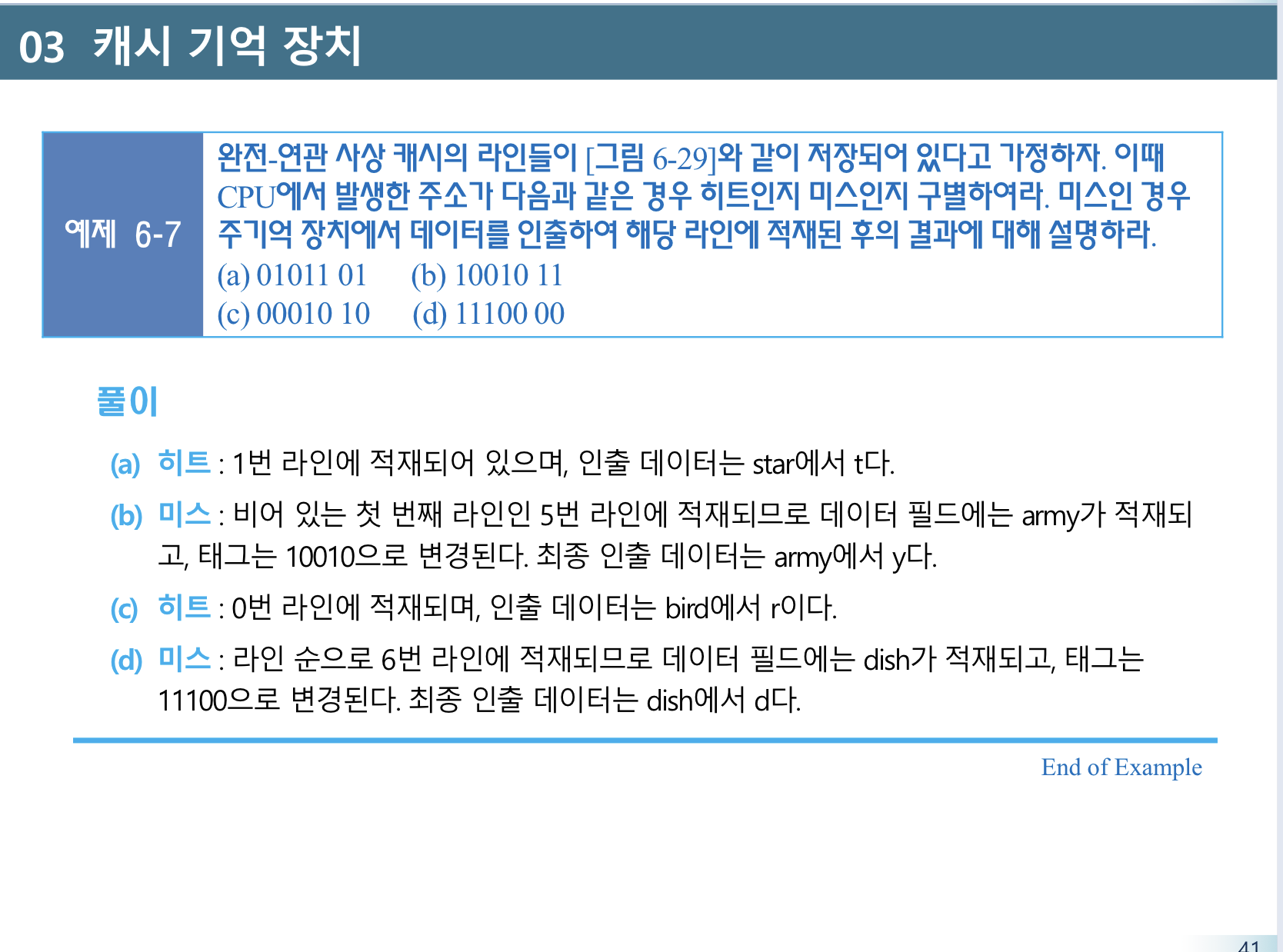

완전 연관 사상 : 캐시에 빈 곳 암데나 넣음. tag로 구분해야 해서 line자리 없고 tag로 다 씀. 주기억장치의 블록번호가 그대로 tag로 쓰임. 나올때까지 처음부터 다 뒤져야 알 수 있음. 빈 자리 없으면 어떻게 쫓아내? → FIFO 등 교체 알고리즘!

세트 연관 사상 : k개의 세트를 가진 k-way연관사상.캐시 라인이 k개의 세트로 나뉨.

교체 알고리즘

- FIFO : 선입선출

- LRU : Least Recently Used → 제일 히트율 좋다고 알려짐

- LFU : Least Frequently Used. 참조되었던 횟수가 가장 적은 방식.

- Random : 임의

쓰기 정책

- Write-through : 모든 쓰기 동작을 캐시와 주기억장치로 동시에 함. 일관성 보장. 시간 소요

- Write-back : 블록이 교체되어 나갈 때 주기억장치에 씀. 캐시슬롯마다 쓰기상태를 나타내는 상태비트 포함.

블록크기가 커질 수록 참조지역성 활용은 좋지만 들어올 수 있는 블록수가 줄어들고 불필요한 워드들도 한방에 가져와야 함.

캐시 수

온 칩 캐시 : cpu칩 내에

계층적 캐시 : 온칩캐시 L1 다음으로 cpu외부에 큰 용량의 2차캐시 L2 둠

평균 장치 액세스 시간 : H1Tc1 + (H2-H1)Tc2 + (1-H2)Tm

분리 캐시 : 명령어/데이터 캐시 분리

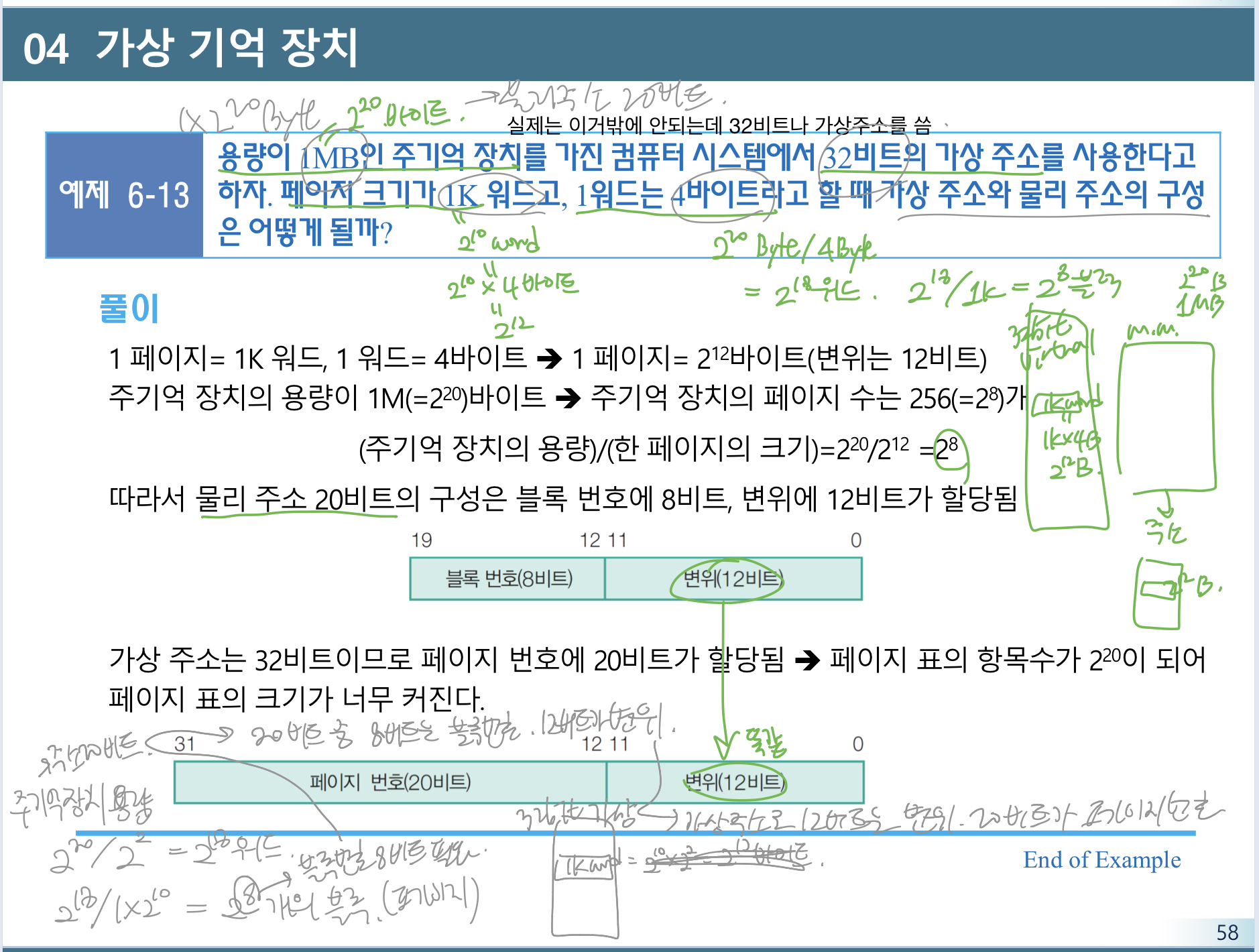

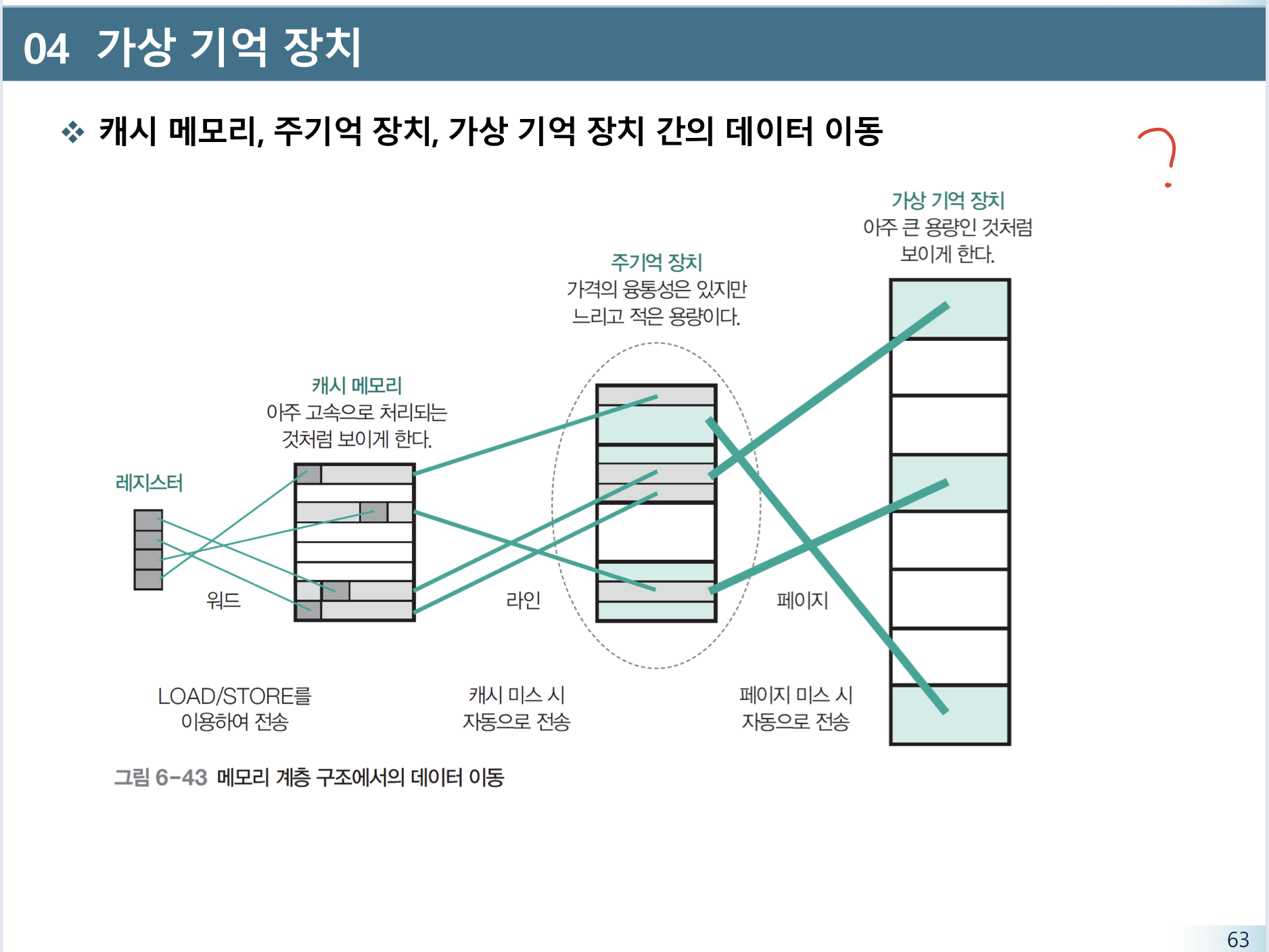

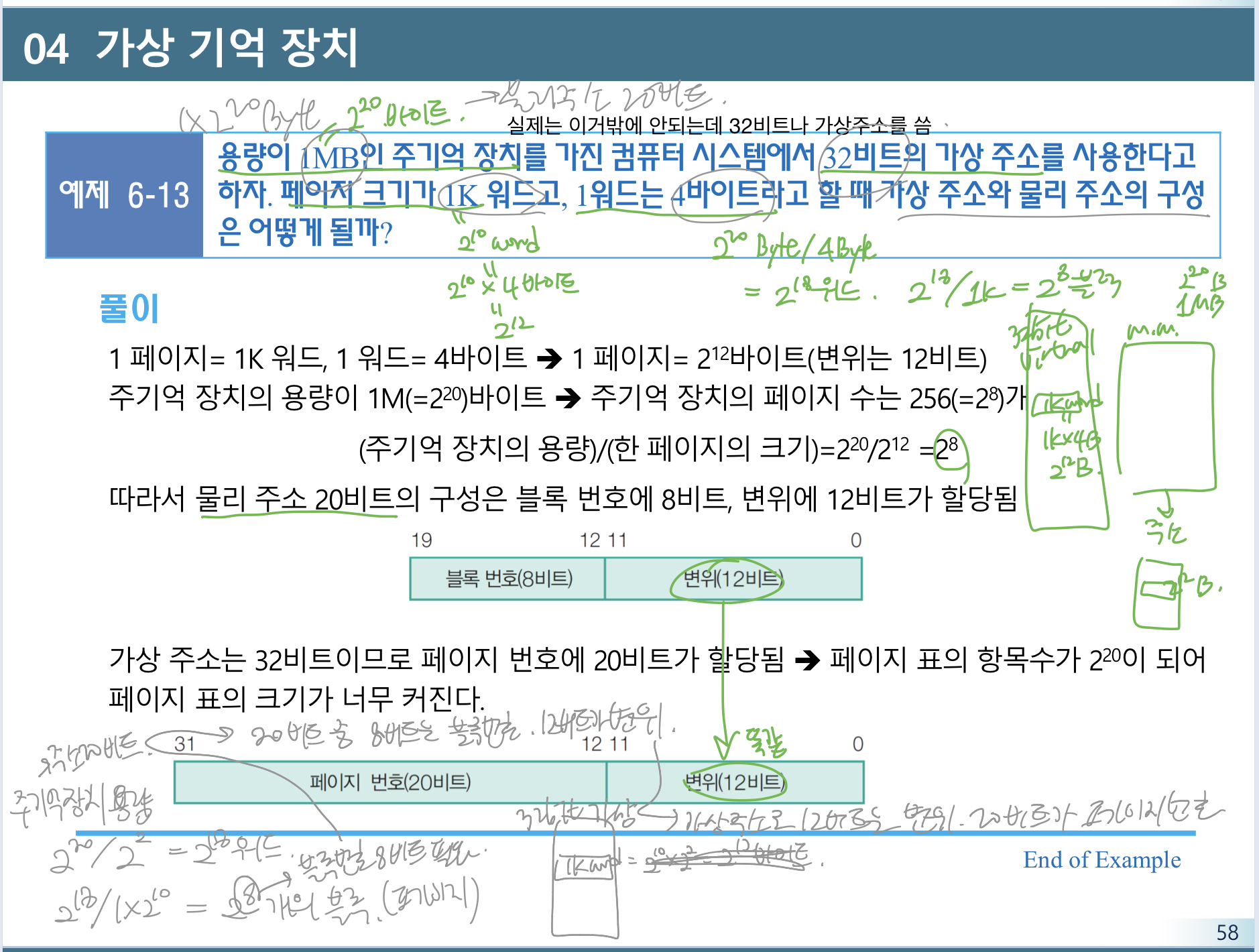

4. 가상기억장치

없는 걸 있는 것처럼. 보조기억장치를 주기억장치처럼 사용함

- 주소 매핑 : cpu의 가상주소를 물리주소로 맵핑 필요

- 가상주소(논리주소) : 프로그램에 사용하는 주소 → 집합 : 주소 공간 → 나눈거 : 페이지

- 물리주소 : 실제 주기억 장치의 주소 → 집합 : 메모리 공간 → 나눈거 : 블록

가상주소 페이지가 주소공간에 존재하지 않을 경우 페이지 오류 발생.

- 기억장치 매핑표(페이지 표) : 페이지 번호에서 블록번호로 변환. 현존비트 1이면 주기억장치에 있는 거

- 연관기억장치 : 페이지 표 항목수가 너무 많을 때 이를 이용해 기억자치를 맵핑함. 페이지 표의 항목을 주기억장치의 블록수로 함. 빠른 비교.

5. 연관기억장치(CAM, 병렬 탐색 기억 장치)

- 저장된 내용의일부를 이용해 저장된 위치를 알아내는 메모리

- 주소접근보다 빠름. 비교회로추가 → 비쌈. 속도가 중요할 때 사용

- 인자 레지스터, 키 레지스터 : 검색하려는 정보, 특정 영역 마스크.

- 페이지표에 사용됨

6. 최신 기억장치 기술

SDRAM(Synchronous DRAM) : DRAM의 액세스를 빠르게 . 시스템 클록에 맞추 동기화 전송.

인터리브드 메모리 : 대역폭을 높이려면? 메모리를 병렬화(메모리의 각 모듈에 주소 지정하고 순차적으로 읽음)하여 액세스 = 인터리빙

액세스 시간을 감소시켜 대역폭 증가의 효과. 블록단위 전송이 가능해 DMA에서 많이 사용.

하위 인터리빙 : 연속된 주소가 연속된 모듈에 나눠져 할당. 다수의 모듈이 동시에 동작 → 액세스 속도 향상

'뚝딱 공부 상자 > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] Chapter8. 버스와 입출력 (0) | 2022.06.25 |

|---|---|

| [컴퓨터 구조] Chapter7. 보조기억장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter5. 제어 장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 04. 중앙 처리 장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 03. 디지털 논리 회로 (0) | 2022.06.25 |

1. 기억장치 시스템 개요

2. 주기억장치

**2KByte = 2 * 2^10 * 8

기억장치 용량 = 2^n * m

→ PC, MAR = n비트

MBR = m비트

주소길이 = n비트. 주소개수 = 2^n

ex) 64KByte RAM = 주소비트가 2^6*2^10 → 16개. 데이터 비트가 8 → 8개

리틀엔디안 : 하위 자리수(바이트)를 낮은 주소에

- ROM(비휘발성. 영구) - 조합회로. 펌웨어저장. 주메모리의 일부 구성

- 마스크 ROM : 제조 시 영구

- PROM : programmable 사용자가 한번 씀. 변경불가

- EPROM : eraseable 자외선으로 복원 가능

- EEPROM : electrically 전기신호로 복원 가능. 플래시메모리(usb.비휘발성 RAM과 입출력가능ROM 장점 동시. 재사용 횟수 제한.)

- RAM(위치관계없이 시간 동일. 휘발성)

- SRAM : 플립플롭. 집적도는 낮으나 비싸고 빠르고 전력많이 먹지만 재충전 필요없어 캐시에 쓰임

- DRAM : 커패시터에 전하 충전. 주기억장치mm

** 위에 바가 있으면 0일 때 동작. CS는 칩 선택 신호. CS와 R/W에 모두 동작신호가 들어와야 동작.

3. 캐시기억장치

캐시 히트율 H

평균 기억장치 액세스 시간 : HTc + (1-H)Tm

참조 지역성

- 공간적 지역성 : 인접

- 시간적 지역성 : 최근 액세스 가까운 미래에 다시 액세스

사상 방식(mapping scheme)

블록은 k개의 워드로 구성. 주기억장치 -블록mapping됨- 캐시 -워드- cpu

캐시가 블록을 갖다놓는데 블록하나가 들어가는 공간이 라인(=frame). 그래서 라인도 k개의 워드로 구성.

tag는 라인에 적재되어있는 블록 구분 정보.

주소는 tag + line + word 구분영역으로 구성(연관사상은line없음)

직접 사상 : 주기억장치의 블록번호에서 앞부분 비트를 태그로 사용하고 뒷부분 비트로 캐시의 어느 라인(frmae)으로 갈 지 직접 정해져 있음. cd, hdd

간단. 비용적음. 같은 라인에 들어갈 블록을 반복적으로 사용하면 히트율 떨어짐

완전 연관 사상 : 캐시에 빈 곳 암데나 넣음. tag로 구분해야 해서 line자리 없고 tag로 다 씀. 주기억장치의 블록번호가 그대로 tag로 쓰임. 나올때까지 처음부터 다 뒤져야 알 수 있음. 빈 자리 없으면 어떻게 쫓아내? → FIFO 등 교체 알고리즘!

세트 연관 사상 : k개의 세트를 가진 k-way연관사상.캐시 라인이 k개의 세트로 나뉨.

교체 알고리즘

- FIFO : 선입선출

- LRU : Least Recently Used → 제일 히트율 좋다고 알려짐

- LFU : Least Frequently Used. 참조되었던 횟수가 가장 적은 방식.

- Random : 임의

쓰기 정책

- Write-through : 모든 쓰기 동작을 캐시와 주기억장치로 동시에 함. 일관성 보장. 시간 소요

- Write-back : 블록이 교체되어 나갈 때 주기억장치에 씀. 캐시슬롯마다 쓰기상태를 나타내는 상태비트 포함.

블록크기가 커질 수록 참조지역성 활용은 좋지만 들어올 수 있는 블록수가 줄어들고 불필요한 워드들도 한방에 가져와야 함.

캐시 수

온 칩 캐시 : cpu칩 내에

계층적 캐시 : 온칩캐시 L1 다음으로 cpu외부에 큰 용량의 2차캐시 L2 둠

평균 장치 액세스 시간 : H1Tc1 + (H2-H1)Tc2 + (1-H2)Tm

분리 캐시 : 명령어/데이터 캐시 분리

4. 가상기억장치

없는 걸 있는 것처럼. 보조기억장치를 주기억장치처럼 사용함

- 주소 매핑 : cpu의 가상주소를 물리주소로 맵핑 필요

- 가상주소(논리주소) : 프로그램에 사용하는 주소 → 집합 : 주소 공간 → 나눈거 : 페이지

- 물리주소 : 실제 주기억 장치의 주소 → 집합 : 메모리 공간 → 나눈거 : 블록

가상주소 페이지가 주소공간에 존재하지 않을 경우 페이지 오류 발생.

- 기억장치 매핑표(페이지 표) : 페이지 번호에서 블록번호로 변환. 현존비트 1이면 주기억장치에 있는 거

- 연관기억장치 : 페이지 표 항목수가 너무 많을 때 이를 이용해 기억자치를 맵핑함. 페이지 표의 항목을 주기억장치의 블록수로 함. 빠른 비교.

5. 연관기억장치(CAM, 병렬 탐색 기억 장치)

- 저장된 내용의일부를 이용해 저장된 위치를 알아내는 메모리

- 주소접근보다 빠름. 비교회로추가 → 비쌈. 속도가 중요할 때 사용

- 인자 레지스터, 키 레지스터 : 검색하려는 정보, 특정 영역 마스크.

- 페이지표에 사용됨

6. 최신 기억장치 기술

SDRAM(Synchronous DRAM) : DRAM의 액세스를 빠르게 . 시스템 클록에 맞추 동기화 전송.

인터리브드 메모리 : 대역폭을 높이려면? 메모리를 병렬화(메모리의 각 모듈에 주소 지정하고 순차적으로 읽음)하여 액세스 = 인터리빙

액세스 시간을 감소시켜 대역폭 증가의 효과. 블록단위 전송이 가능해 DMA에서 많이 사용.

하위 인터리빙 : 연속된 주소가 연속된 모듈에 나눠져 할당. 다수의 모듈이 동시에 동작 → 액세스 속도 향상

'뚝딱 공부 상자 > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] Chapter8. 버스와 입출력 (0) | 2022.06.25 |

|---|---|

| [컴퓨터 구조] Chapter7. 보조기억장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter5. 제어 장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 04. 중앙 처리 장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 03. 디지털 논리 회로 (0) | 2022.06.25 |