목차

반응형

1. 논리 게이트

TTL COMS어쩌구..

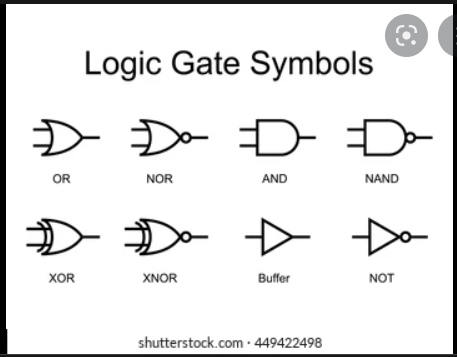

종류

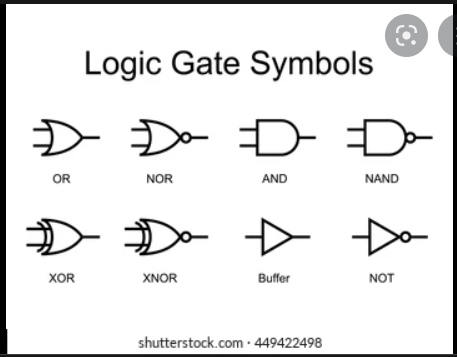

세가지만 기억 - 버퍼 삼각형, and 동글, or 뾰족, xor )

- 버퍼 게이트 : 그대로.

- 3상태 버퍼 : E가 1이면 통과, 0이면 차단(하이임피던스). Enable값에 따라 0,1, 하이임피던스 3가지 결과.

- NOT(inverter)

- AND / NAND

- OR / NOR

- XOR 다르면 1!!! / NXOR

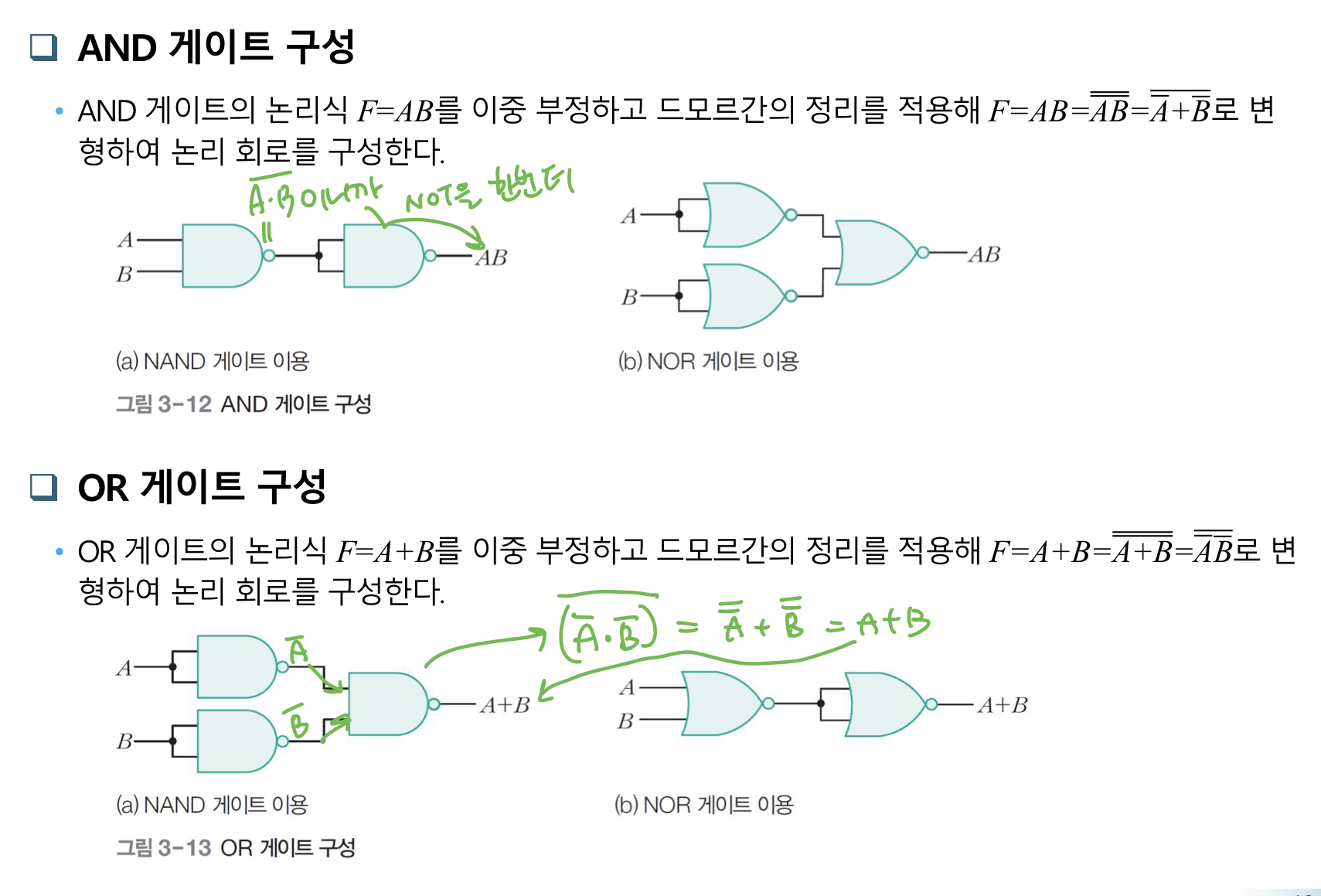

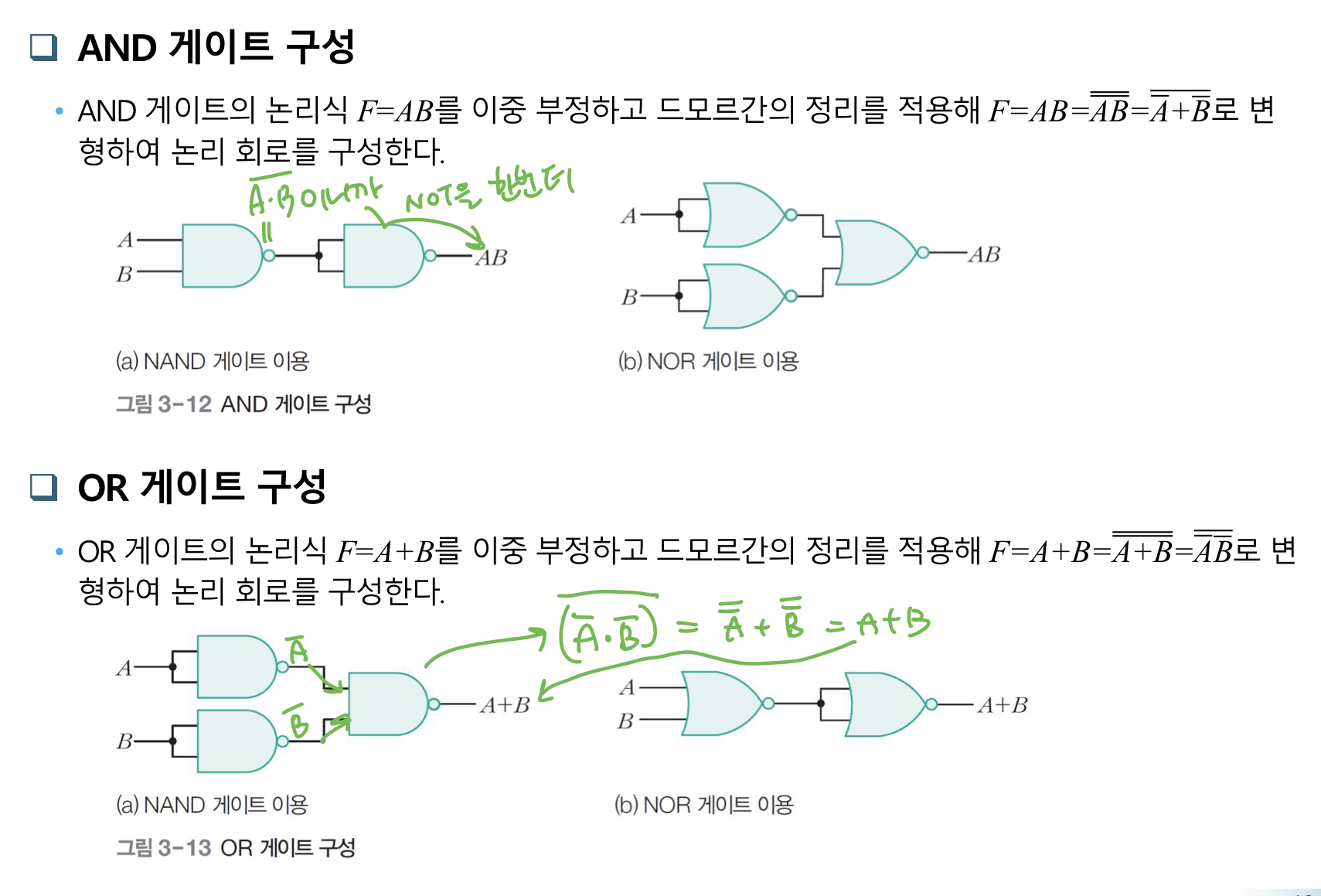

- 유니버설 게이트 : NAND, NOR 만 있으면 모든 회로 만들 수 있음

2. 불 대수

and는 곱, or는 덧셈, not은 —나 ‘ 로 표현

불 대수 법칙

- 모든 항은 0또는 1을 의미함

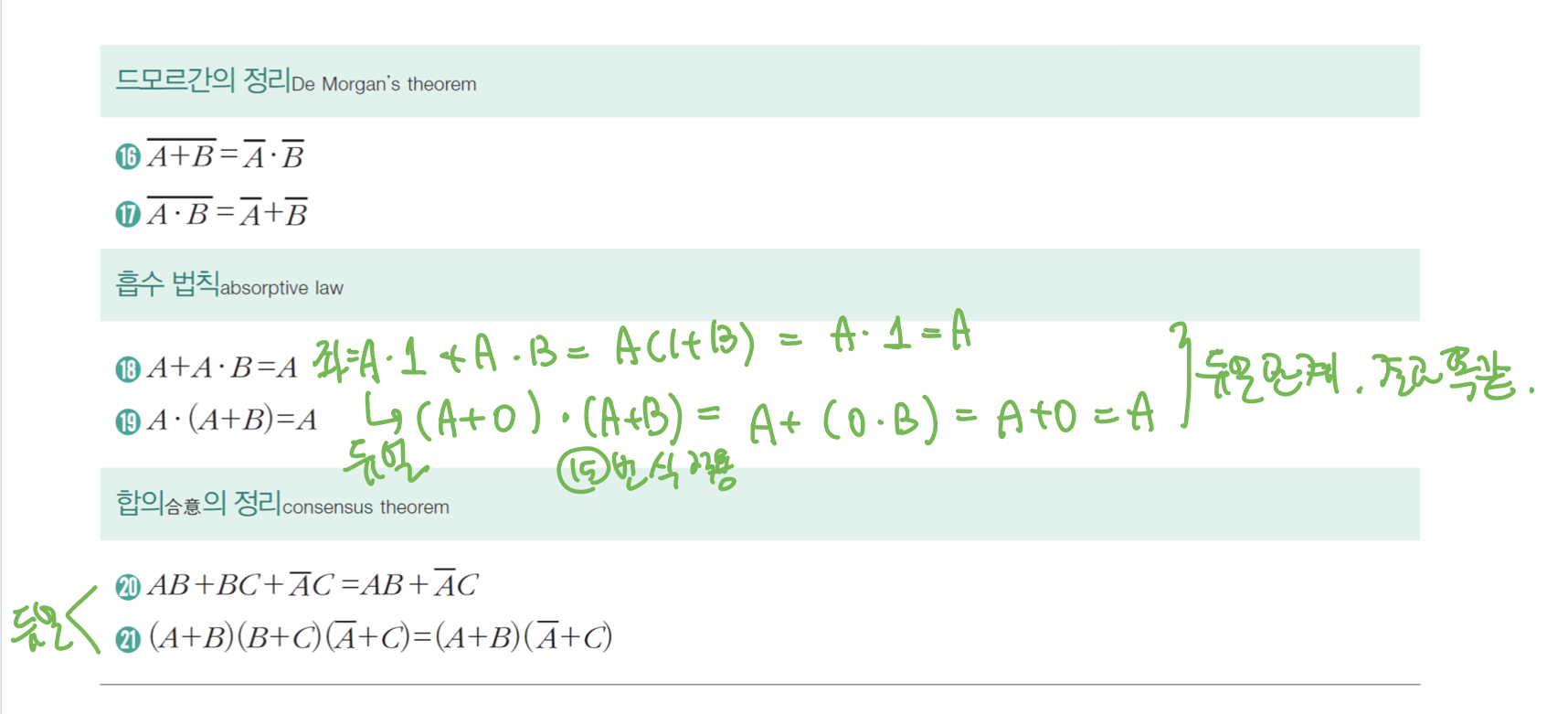

- dual 쌍대성 : 전체 식을 0↔1, +↔* 로 바꾸면 그 식도 성립함

- 논리대수의 분배법칙 - 헷갈리면 듀얼로 확인가능

- 곱에 대해 합이 분배됨 : A+(B*C) = (A+B) * (A+C)

- 합에 대해 곱 분배도 성립!! : A*(B+C) = AC + BC

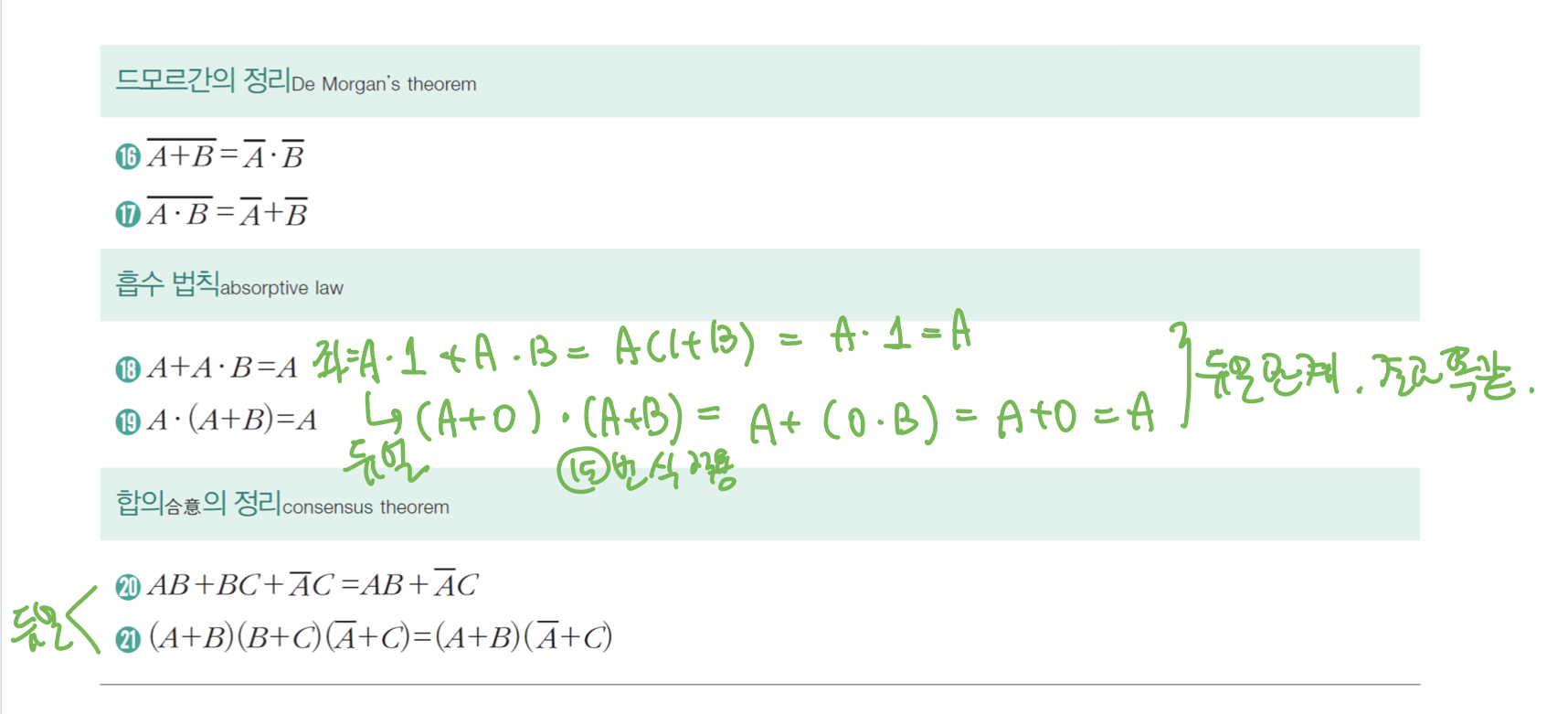

- 드모르간 정리 : 전체 not은 식의 부호를 바꾼 후 개별 not으로 바꿀 수 있음

- 흡수 법칙 : aa+b = a, a+ab = a - ??ㅋㅋㅋ

- 합의의 정리 -????

- 부울식의 표준형 → 이렇게 표현해야 논리회로 그림이 2단으로 깔끔하게 나온다.

- SOP(sum of products) 곱의 합 : ABC + AB

- POS(product of sums) 합의 곱 : (A+B)*(A+C)

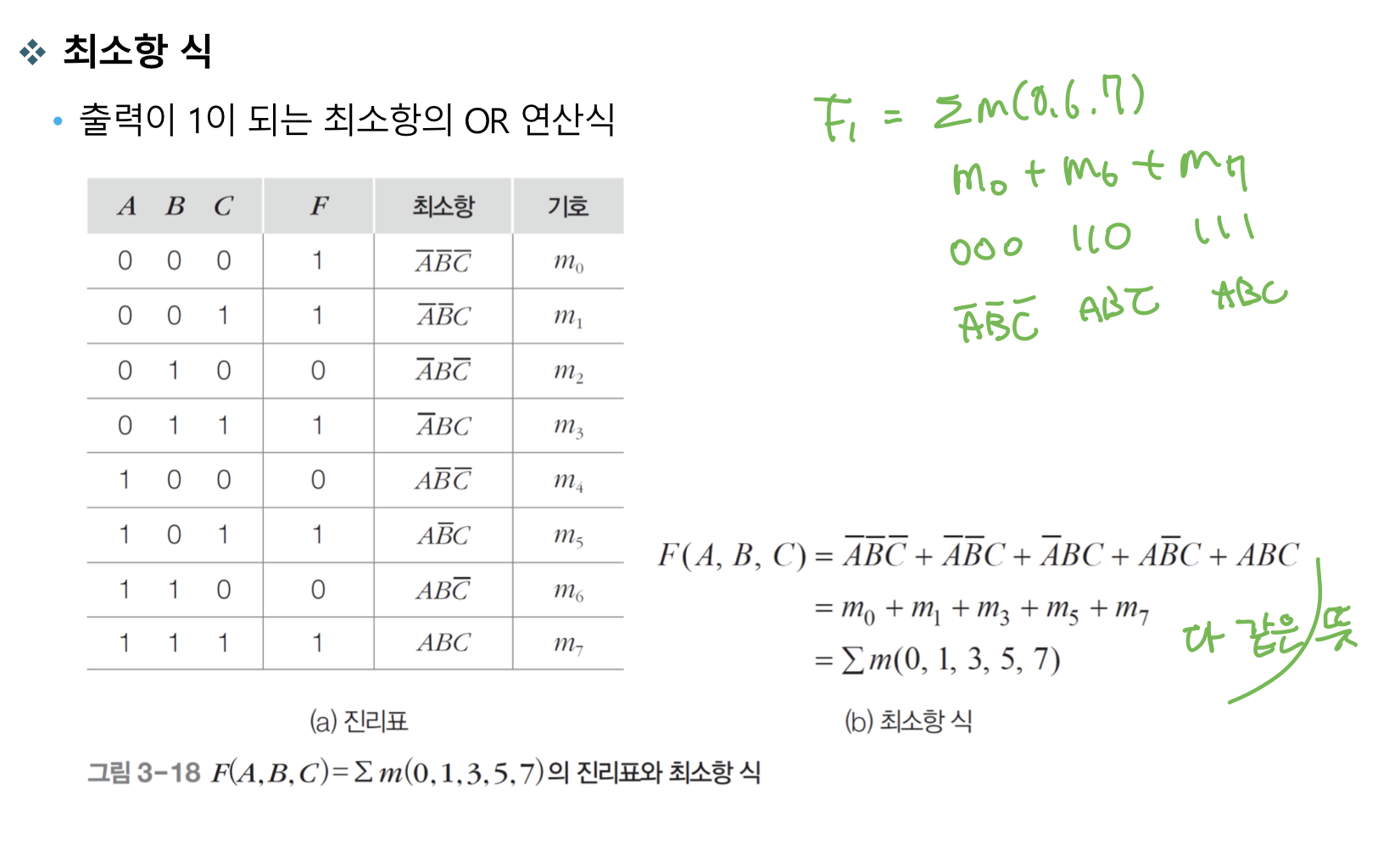

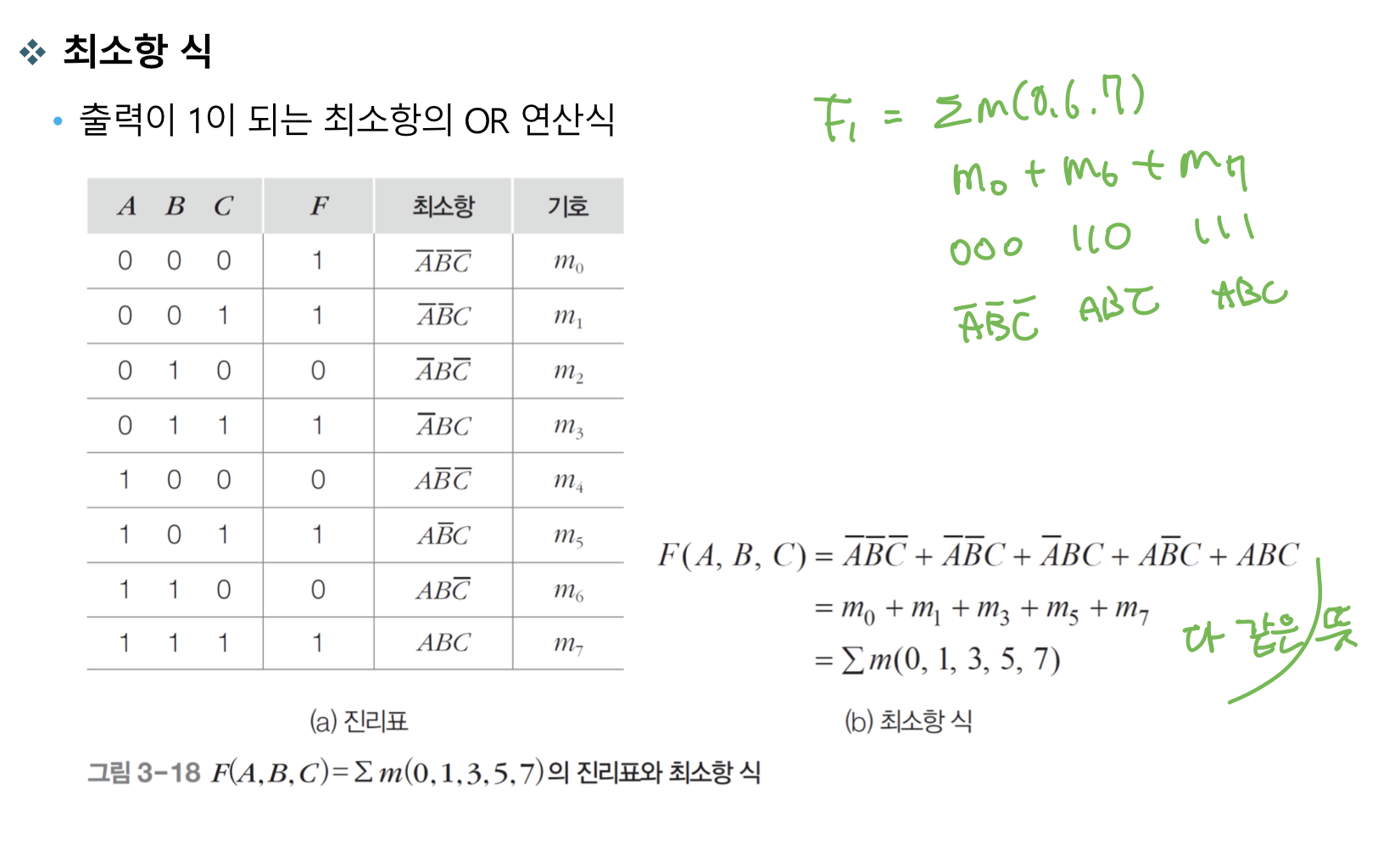

- 최소항minterm : 각 자리가 0이면 해당 입력변수의 not을 의미함. 곱으로 연결

- 최대항maxterm : 합으로 연결! 최소항 반대. 1이면 not.

- 최소항과 최대항은 서로 보수의 성질.

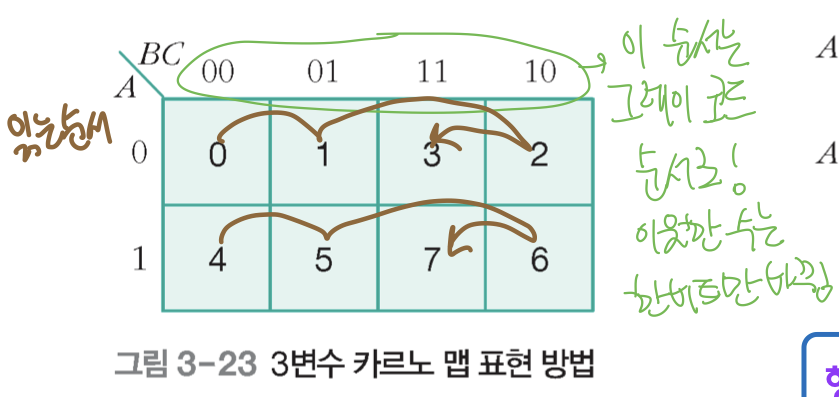

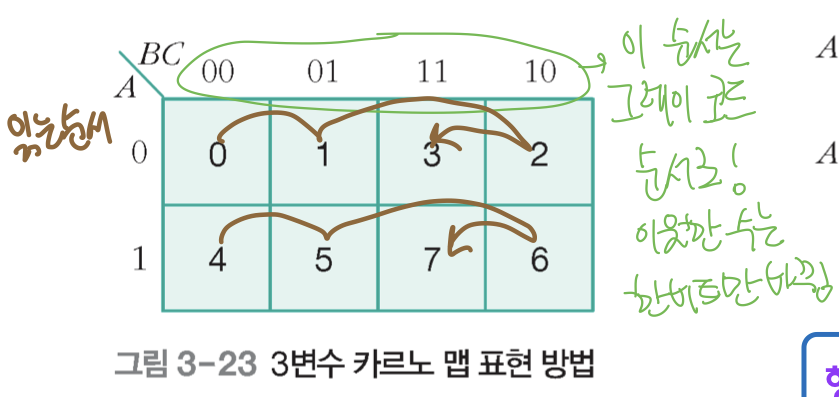

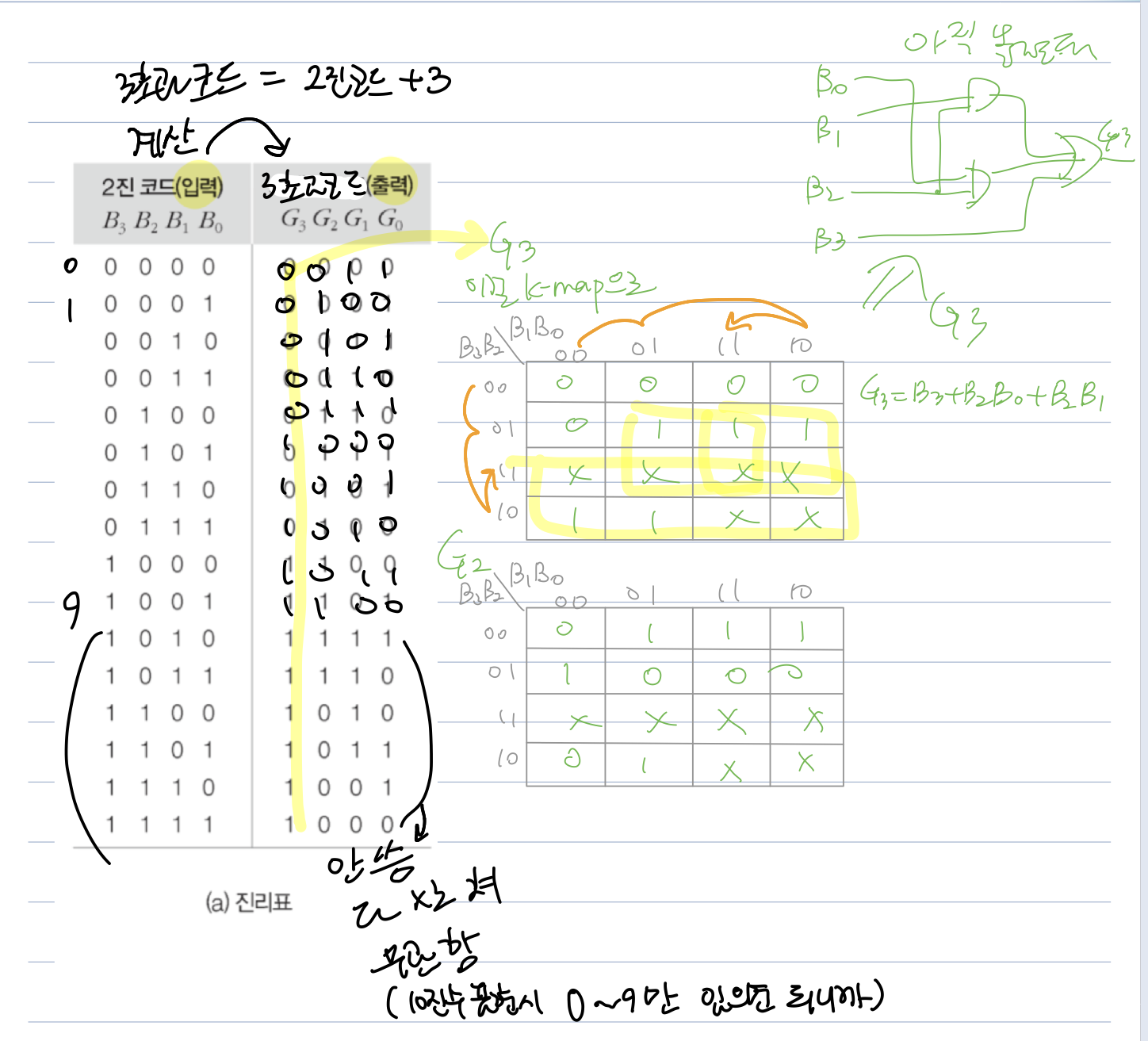

- 논리식 간소화k-map카르노맵을 사용함

- 불 대수 법칙을 이용한 논리식이 간소화는 복잡함. k-map카르노맵을 사용함

- 카르노맵

- X무관항 : 맘대로 써라

3. 조합 논리 회로

분류

- 조합 논리 회로 : 입력에 따른 출력

- 순차(순서)회로 : 시간 개념 고려

조합 논리 회로 종류

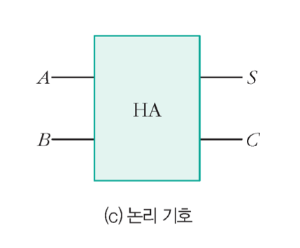

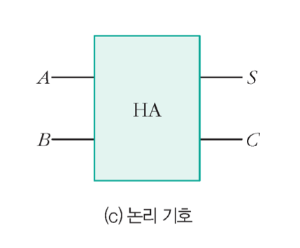

- HA반가산기 : 1자리 이진수 2개 계산 (총 2개) → 합S와 캐리C 결과냄 (총 2개)

- but 실제로는 여러자리 연산을 하므로 이전 자릿수에서 올라온 캐리input 받기 필요 → 불완전함

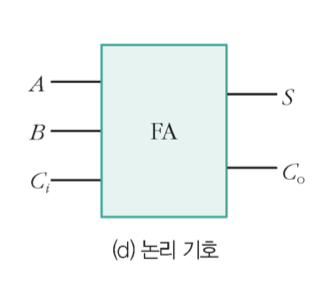

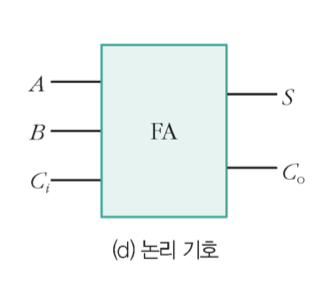

- FA전가산기 : 입력 2개, 캐리입력 1개 (총 3개) → 합S와 캐리C 결과냄 (총 2개)

- 온전한 가산기. 이걸 조합해서 사용함

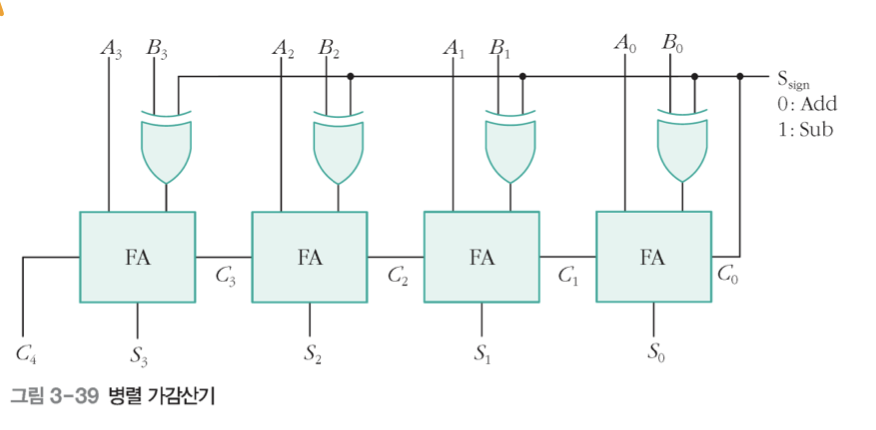

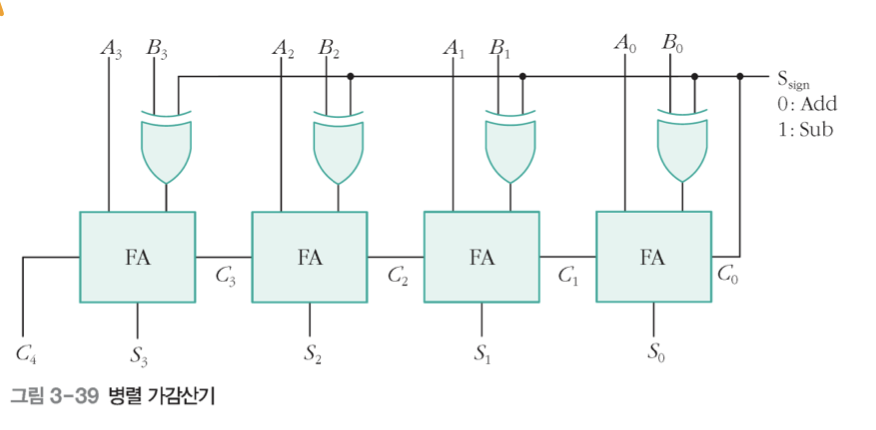

- ★병렬 가감산기 : 덧셈 뺄셈 선택 가능. 전가산기 여러개 병렬 연결(캐리 지연시간이 있어 진정한 동시입력 병렬은 아님)

- C0에는 직전자리 캐리가 없으므로 양수는 0, 음수는1로 채워준다.

- 이진 비교기 : 크기비교

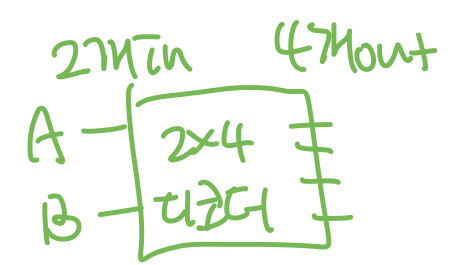

- 디코더decoder : n비트의 이진코드를 2^n개의 정보로 해독해줌. 출력 여러개 중 단 하나만 1. 그걸로 해독(선택)된 것임

- 인코더encoder(부호기) : 코드 만들어줌~ 2^n개중 단 하나만 1인 신호를 받아 그에 해당하는 n비트 2진 코드를 출력함

- 1이 실수로 여러개 들어가면 큰일남 → 우선순위 인코더 사용

- 우선순위 인코더 : 뒷자리에 1이 나오면 앞에 나왔던 1들은 그냥 무시함~~ 1010 → 0010

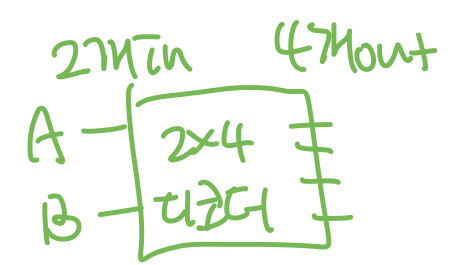

- 멀티플렉서MUX : 입력 여러개, 이 중 하나만 선택해서 단 하나 있는 출력선에 연결함(값 전달함).

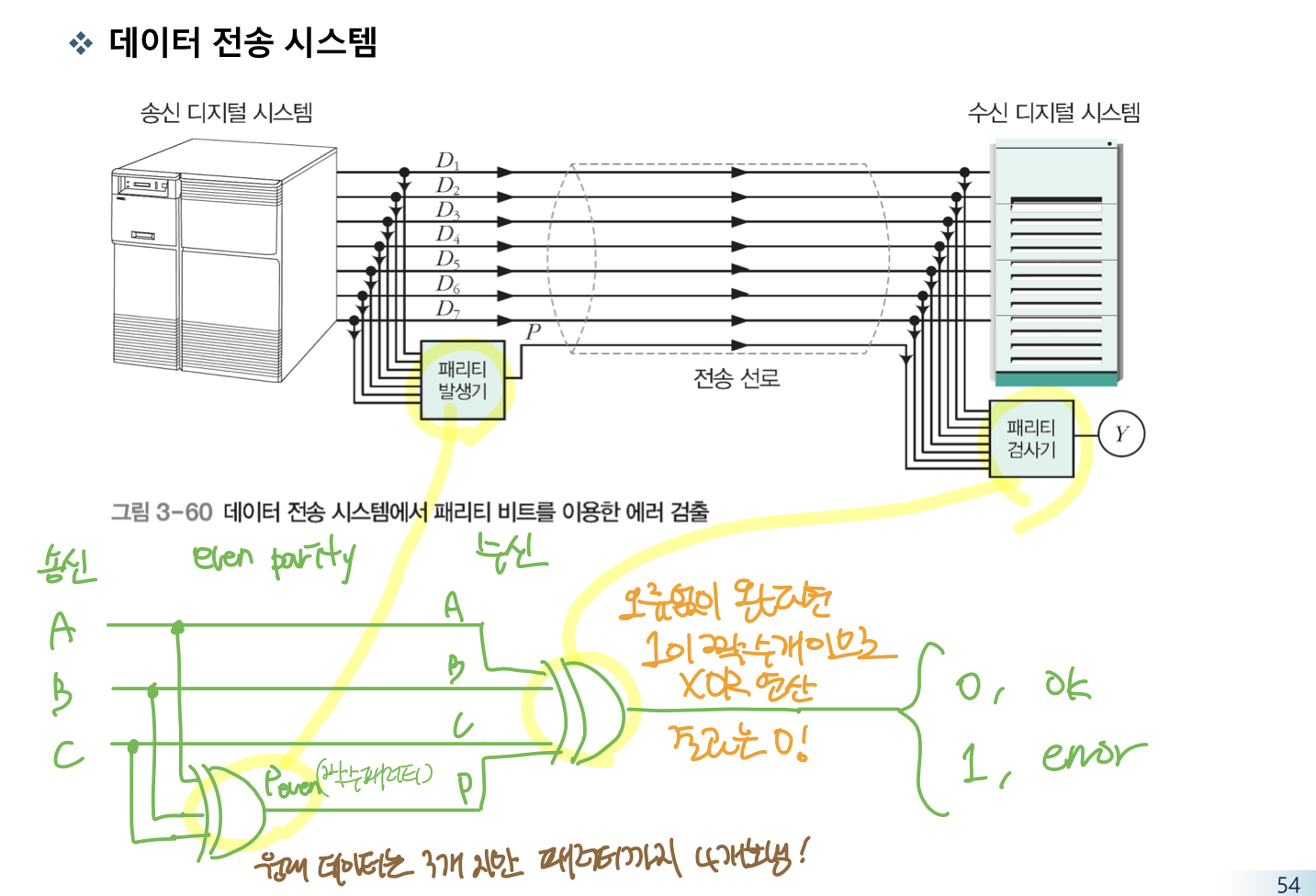

- 2^n개의 입력 중 하나를 선택하려면 n개의 선택신호선 필요!

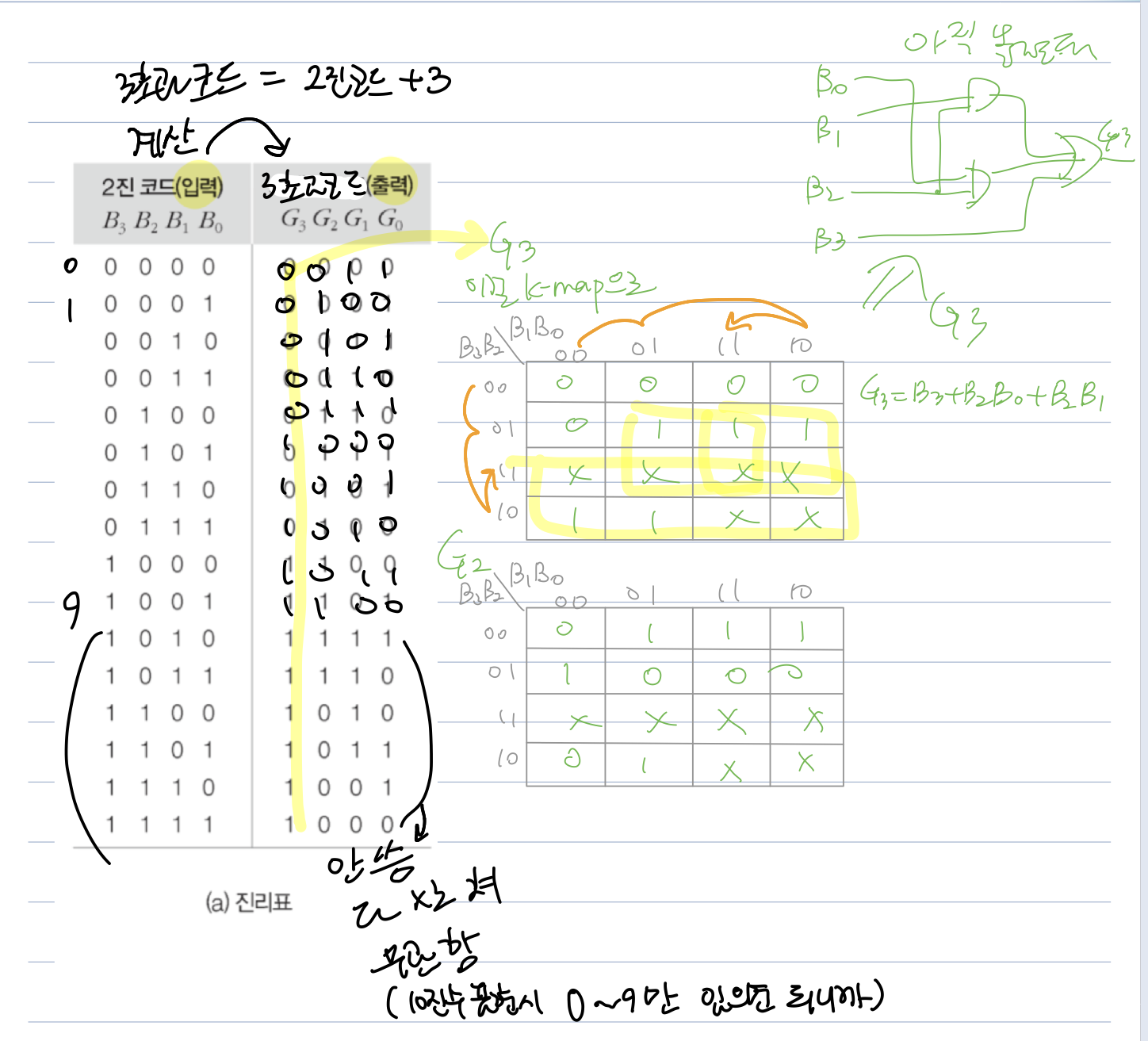

- 코드 변환기 -??

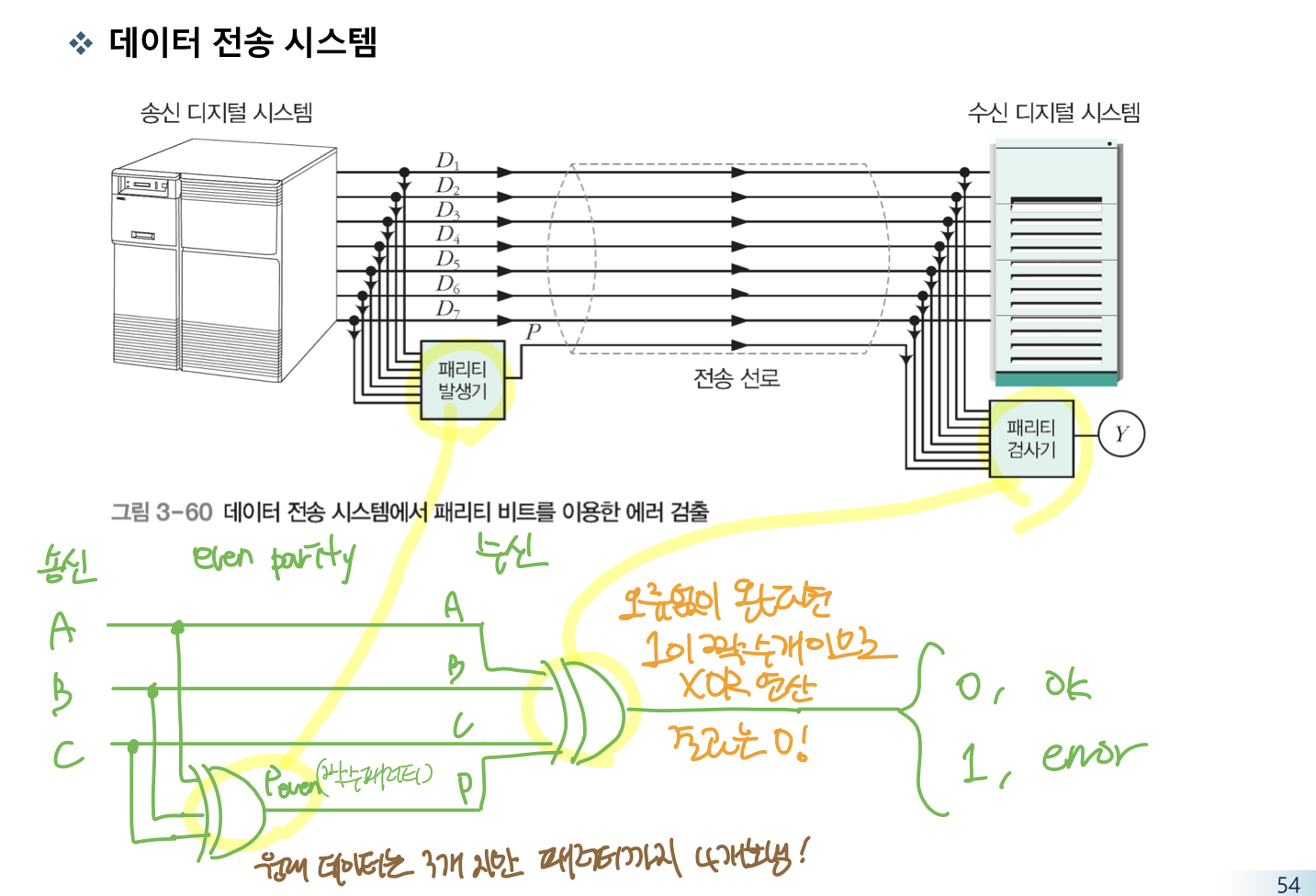

- 짝/홀수 패러티 발생기 : 입력에 대해 1을 짝/홀수개로 패리티비트 설정

- XOR게이트와 성질 동일. 이용.

- 패리티 검사기 : 1이면 에러 있음(1이 짝/홀수개 아님).

4. 순서 논리 회로

시간 개념 필요 → 클록펄스Clock Pulse

현재 입력값 & 이전 출력값에 따라 출력값 결정됨

- 클록펄스

- 출력은 클럭펄스에 동기되어 변함. 상승 또는 하강엣지의 순간에 변하는 것을 트리거되었다고 함

- 플립플롭FF : 1비트 저장소. 다음 클록펄스가 들어올 때까지 상태유지. Q Q’ 출력 두개 서로 보수여야 정상상태임.

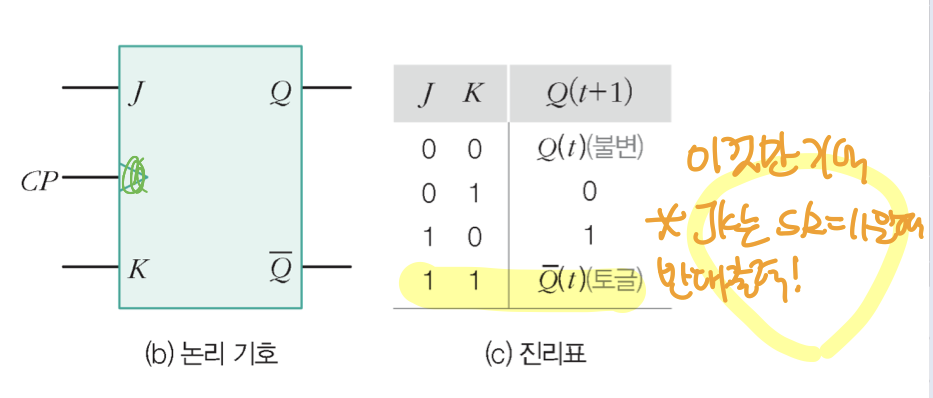

플립플롭 종류

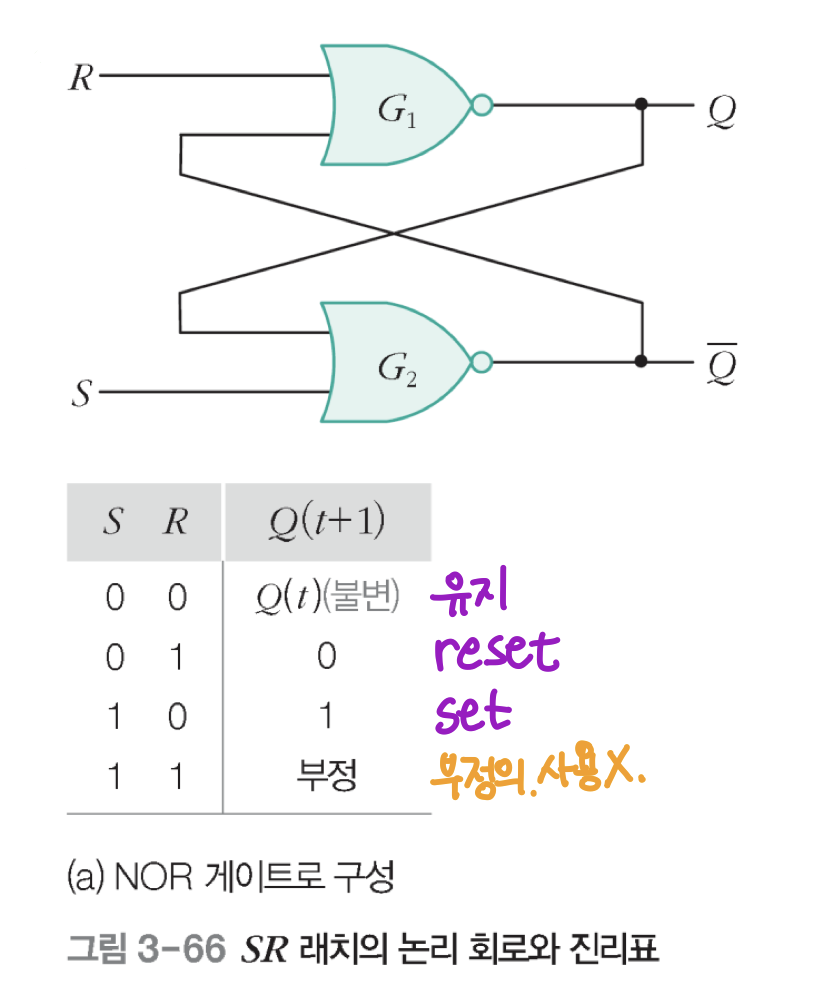

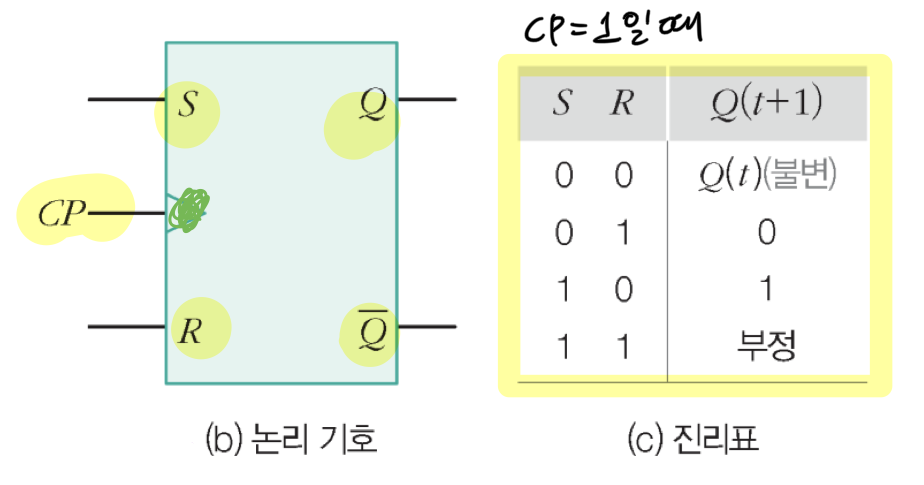

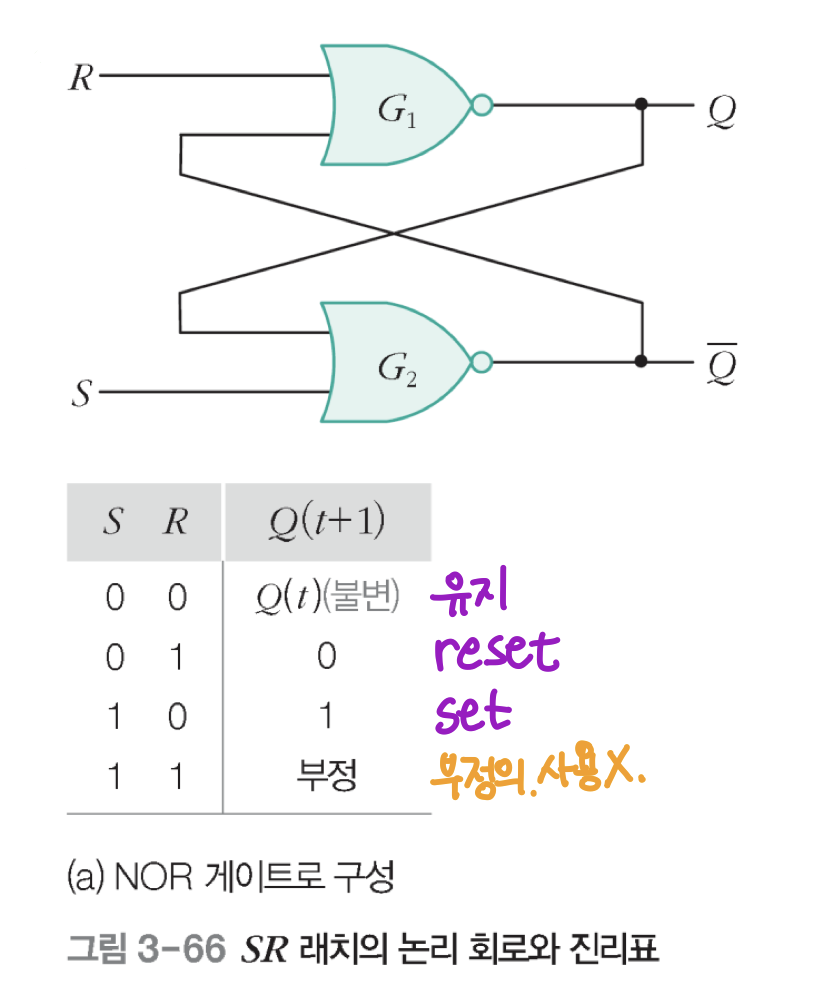

- SR래치 (Set Reset)

- 불변 ⇒ 메모리의 개념

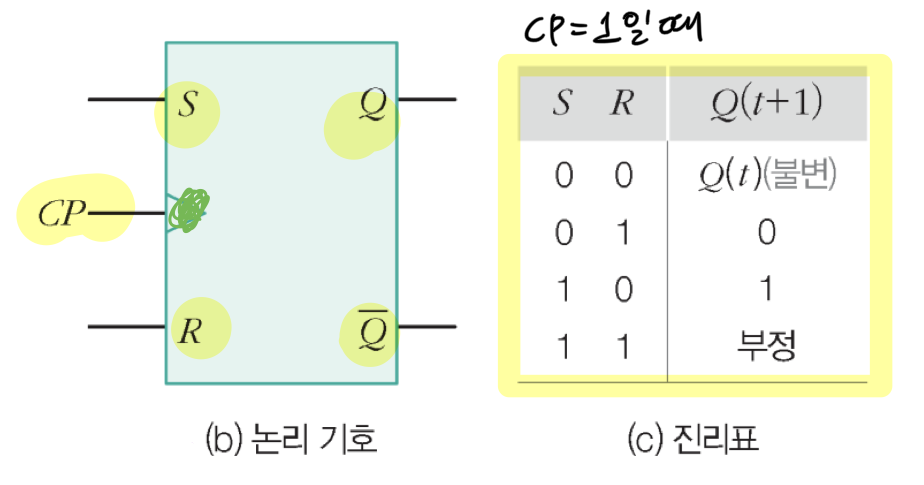

- SR FF플립플롭 : CP=1일 때만 동작하는 SR래치! CP=0이면 이전값을 유지함.

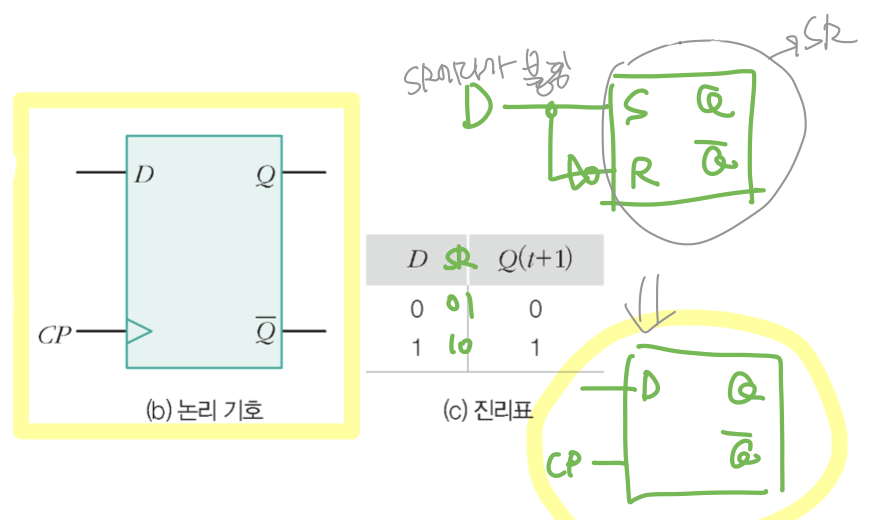

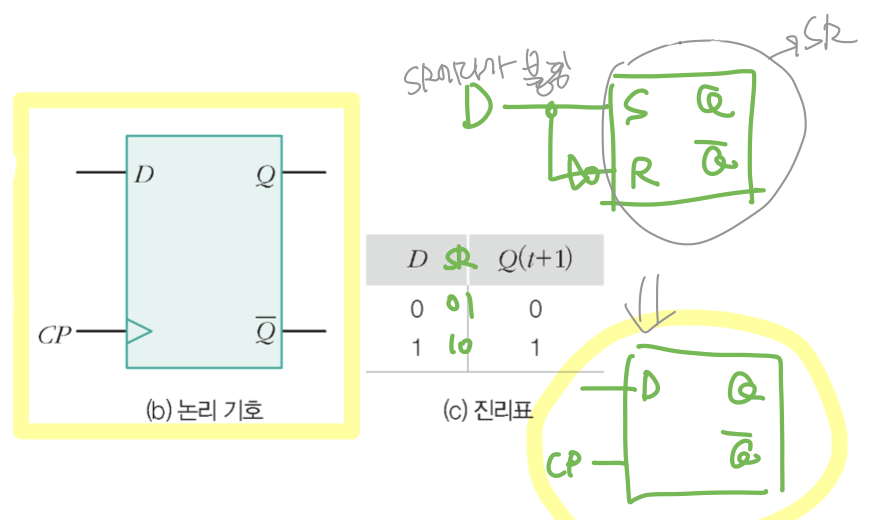

- D FF플립플롭(Delay)지연시킨 후 다음 클럭에 전달되도록 함

- SR FF에서 SR=11을 제거. D만 가지고 D’과 입력으로 사용함.

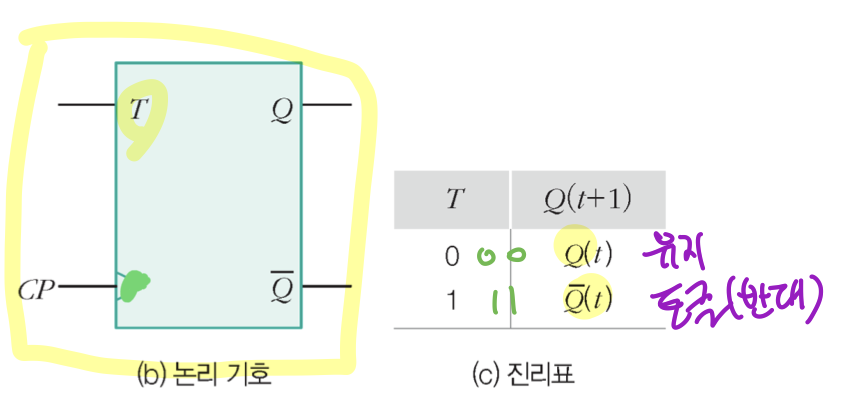

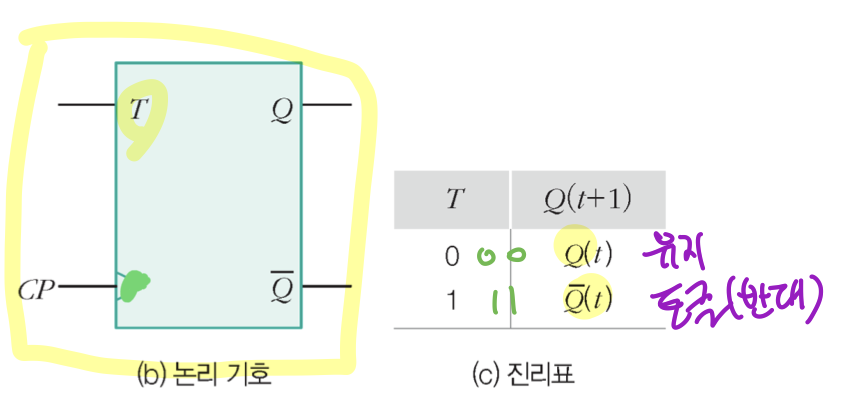

- T FFJ=K=0이면 유지, J=K=1이면 보수.

- D FF와 반대. 이건 SR=00과 SR=11만 있음

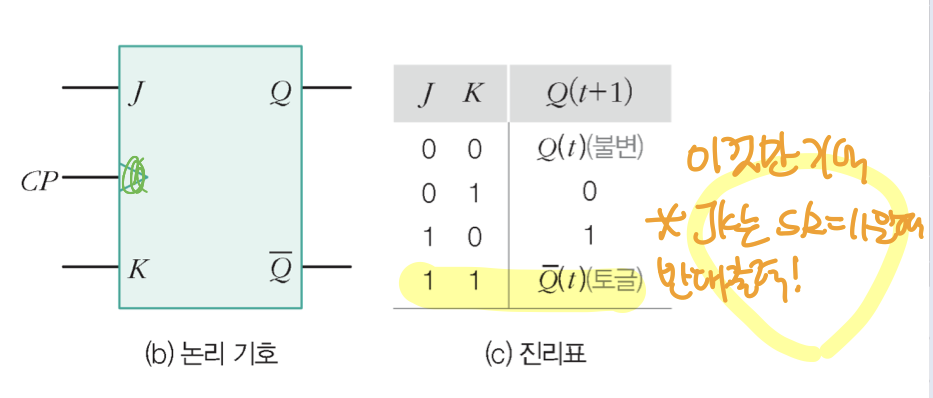

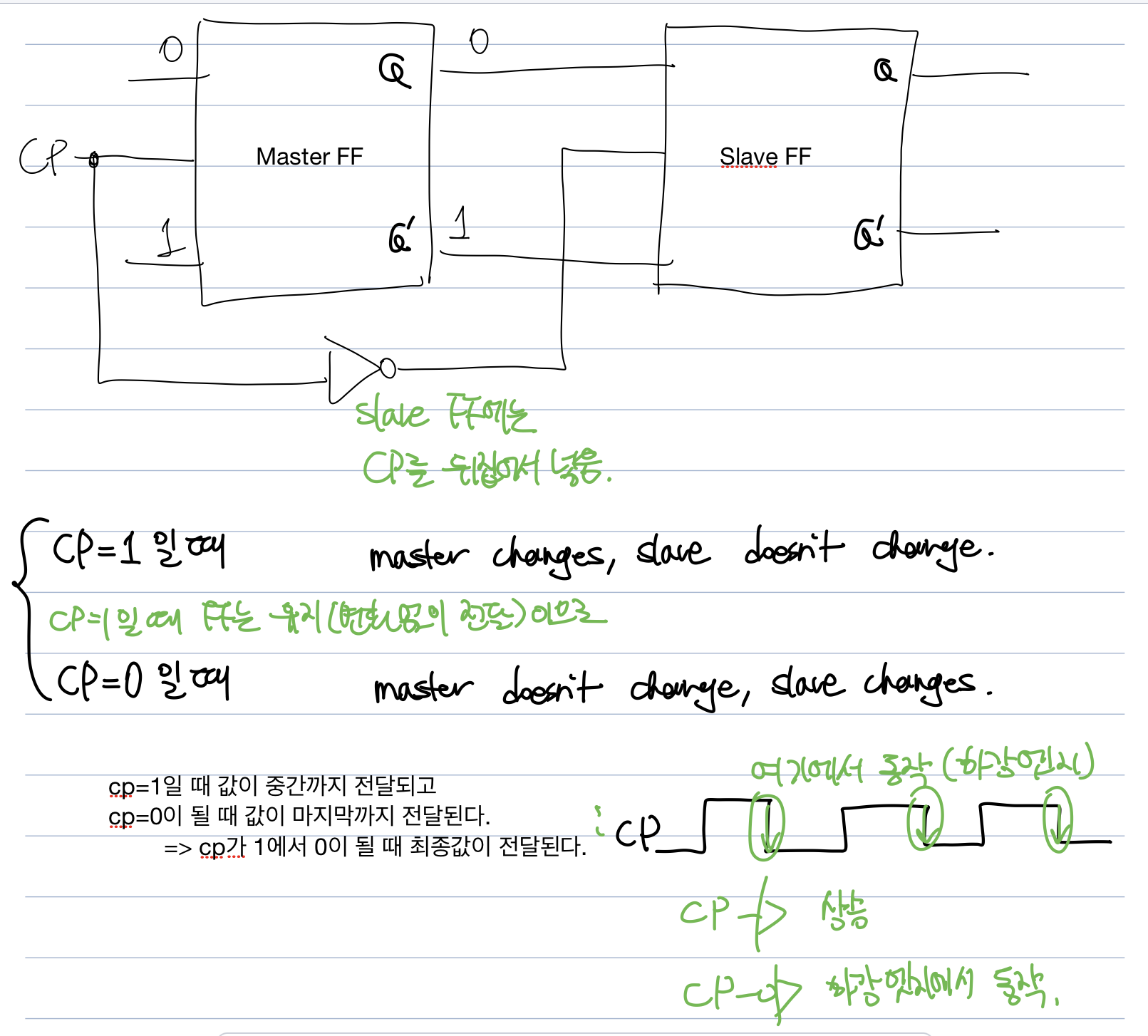

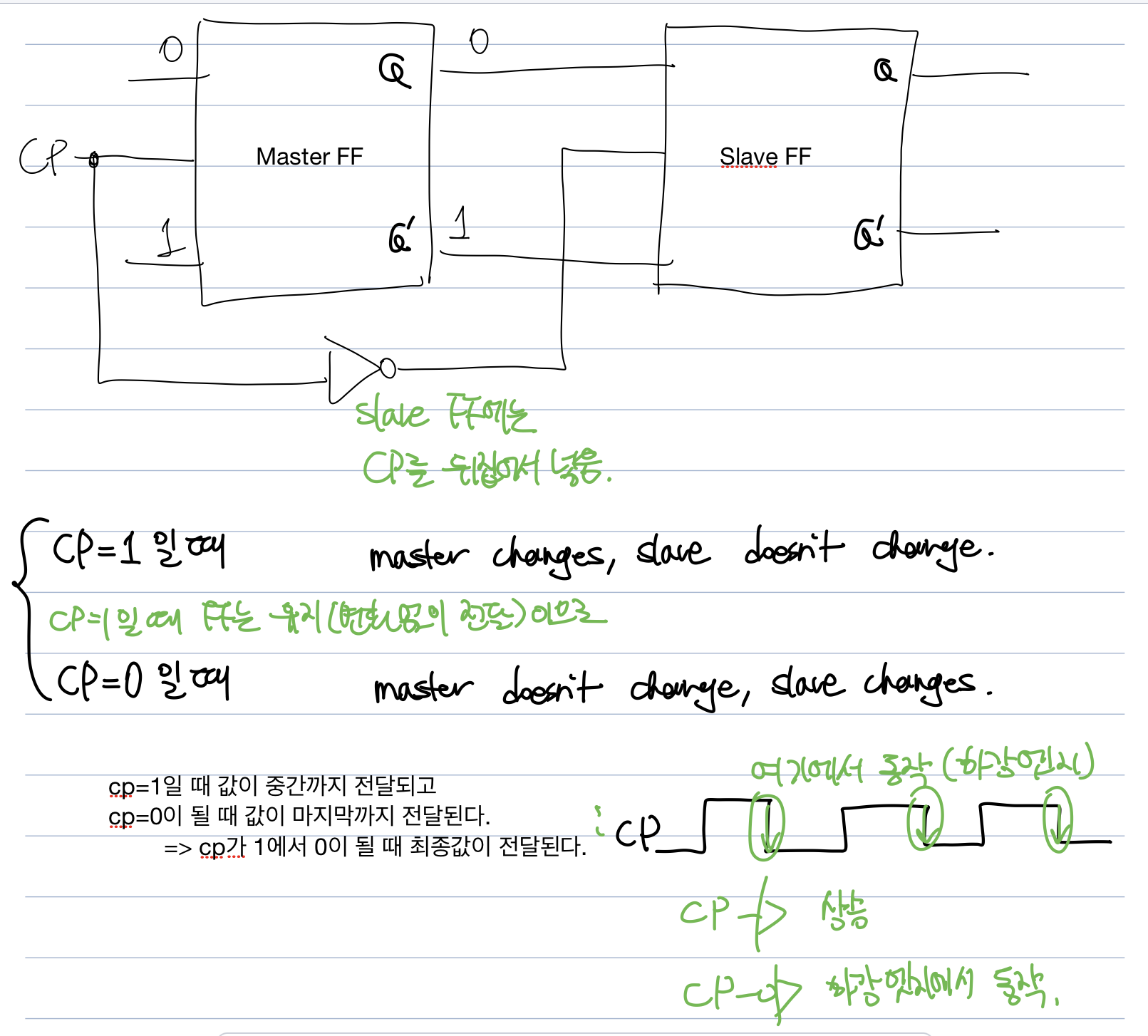

- JK FF플립플롭JK=11이면 이전출력의 보수를 출력함** 레이스 현상 문제 : CP=1, JK=11이면 무한히 반전값이 나오는 문제점 → 해결하자 주종형 JK

- 가장 많이 사용됨

- SR FF 에서 SR=JK=11일때도 동작하도록 만듦.

- 주종형 JK FF

- 레이스 현상 문제 해결. 하강엣지에서 동작함!

- 비동기 입력 : 클럭펄스와 관계없이 변화시킬 수 있는 입력

- 여기표 : 이러한 현재상태에서 저러한 다음상태로 가려면 입력엔 뭘 넣어야 하나?

레지스터

FF를 n개 모은 n비트 저장소! CP클록펄스가 공통으로 들어감

- 4비트 병렬 레지스터 : 공통 클럭 신호의 상승엣지에서 입력4개가 D FF 4개에 동시저장

- 시프트 레지스터 : CP가 있을 때마다 입력데이터가 한 비트씩 옆으로 옮겨가며 저장

- 카운터 : CP에 따라 수를 셈

- 동기식 : CP에 동기화되어 FF가 동시 동작

- 비동기식(리플 카운터) : 다른 FF의 출력을 CP로 사용함. 각 FF는 CP의 하강엣지에서 변함.

5. 집적 회로

칩. Integrated Circuit. IC.

컴퓨터 3세대 → IC등장

4세대 → VLSI 초대규모직접회로 등장

직접회로의 발전으로

- 소비 전력 감소

- 고속화 신뢰도 저렴화 경량화

반응형

'뚝딱 공부 상자 > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] Chapter6. 기억장치 (0) | 2022.06.25 |

|---|---|

| [컴퓨터 구조] Chapter5. 제어 장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 04. 중앙 처리 장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 02. 데이터의 표현 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 01. 서론 (0) | 2022.06.25 |

반응형

1. 논리 게이트

TTL COMS어쩌구..

종류

세가지만 기억 - 버퍼 삼각형, and 동글, or 뾰족, xor )

- 버퍼 게이트 : 그대로.

- 3상태 버퍼 : E가 1이면 통과, 0이면 차단(하이임피던스). Enable값에 따라 0,1, 하이임피던스 3가지 결과.

- NOT(inverter)

- AND / NAND

- OR / NOR

- XOR 다르면 1!!! / NXOR

- 유니버설 게이트 : NAND, NOR 만 있으면 모든 회로 만들 수 있음

2. 불 대수

and는 곱, or는 덧셈, not은 —나 ‘ 로 표현

불 대수 법칙

- 모든 항은 0또는 1을 의미함

- dual 쌍대성 : 전체 식을 0↔1, +↔* 로 바꾸면 그 식도 성립함

- 논리대수의 분배법칙 - 헷갈리면 듀얼로 확인가능

- 곱에 대해 합이 분배됨 : A+(B*C) = (A+B) * (A+C)

- 합에 대해 곱 분배도 성립!! : A*(B+C) = AC + BC

- 드모르간 정리 : 전체 not은 식의 부호를 바꾼 후 개별 not으로 바꿀 수 있음

- 흡수 법칙 : aa+b = a, a+ab = a - ??ㅋㅋㅋ

- 합의의 정리 -????

- 부울식의 표준형 → 이렇게 표현해야 논리회로 그림이 2단으로 깔끔하게 나온다.

- SOP(sum of products) 곱의 합 : ABC + AB

- POS(product of sums) 합의 곱 : (A+B)*(A+C)

- 최소항minterm : 각 자리가 0이면 해당 입력변수의 not을 의미함. 곱으로 연결

- 최대항maxterm : 합으로 연결! 최소항 반대. 1이면 not.

- 최소항과 최대항은 서로 보수의 성질.

- 논리식 간소화k-map카르노맵을 사용함

- 불 대수 법칙을 이용한 논리식이 간소화는 복잡함. k-map카르노맵을 사용함

- 카르노맵

- X무관항 : 맘대로 써라

3. 조합 논리 회로

분류

- 조합 논리 회로 : 입력에 따른 출력

- 순차(순서)회로 : 시간 개념 고려

조합 논리 회로 종류

- HA반가산기 : 1자리 이진수 2개 계산 (총 2개) → 합S와 캐리C 결과냄 (총 2개)

- but 실제로는 여러자리 연산을 하므로 이전 자릿수에서 올라온 캐리input 받기 필요 → 불완전함

- FA전가산기 : 입력 2개, 캐리입력 1개 (총 3개) → 합S와 캐리C 결과냄 (총 2개)

- 온전한 가산기. 이걸 조합해서 사용함

- ★병렬 가감산기 : 덧셈 뺄셈 선택 가능. 전가산기 여러개 병렬 연결(캐리 지연시간이 있어 진정한 동시입력 병렬은 아님)

- C0에는 직전자리 캐리가 없으므로 양수는 0, 음수는1로 채워준다.

- 이진 비교기 : 크기비교

- 디코더decoder : n비트의 이진코드를 2^n개의 정보로 해독해줌. 출력 여러개 중 단 하나만 1. 그걸로 해독(선택)된 것임

- 인코더encoder(부호기) : 코드 만들어줌~ 2^n개중 단 하나만 1인 신호를 받아 그에 해당하는 n비트 2진 코드를 출력함

- 1이 실수로 여러개 들어가면 큰일남 → 우선순위 인코더 사용

- 우선순위 인코더 : 뒷자리에 1이 나오면 앞에 나왔던 1들은 그냥 무시함~~ 1010 → 0010

- 멀티플렉서MUX : 입력 여러개, 이 중 하나만 선택해서 단 하나 있는 출력선에 연결함(값 전달함).

- 2^n개의 입력 중 하나를 선택하려면 n개의 선택신호선 필요!

- 코드 변환기 -??

- 짝/홀수 패러티 발생기 : 입력에 대해 1을 짝/홀수개로 패리티비트 설정

- XOR게이트와 성질 동일. 이용.

- 패리티 검사기 : 1이면 에러 있음(1이 짝/홀수개 아님).

4. 순서 논리 회로

시간 개념 필요 → 클록펄스Clock Pulse

현재 입력값 & 이전 출력값에 따라 출력값 결정됨

- 클록펄스

- 출력은 클럭펄스에 동기되어 변함. 상승 또는 하강엣지의 순간에 변하는 것을 트리거되었다고 함

- 플립플롭FF : 1비트 저장소. 다음 클록펄스가 들어올 때까지 상태유지. Q Q’ 출력 두개 서로 보수여야 정상상태임.

플립플롭 종류

- SR래치 (Set Reset)

- 불변 ⇒ 메모리의 개념

- SR FF플립플롭 : CP=1일 때만 동작하는 SR래치! CP=0이면 이전값을 유지함.

- D FF플립플롭(Delay)지연시킨 후 다음 클럭에 전달되도록 함

- SR FF에서 SR=11을 제거. D만 가지고 D’과 입력으로 사용함.

- T FFJ=K=0이면 유지, J=K=1이면 보수.

- D FF와 반대. 이건 SR=00과 SR=11만 있음

- JK FF플립플롭JK=11이면 이전출력의 보수를 출력함** 레이스 현상 문제 : CP=1, JK=11이면 무한히 반전값이 나오는 문제점 → 해결하자 주종형 JK

- 가장 많이 사용됨

- SR FF 에서 SR=JK=11일때도 동작하도록 만듦.

- 주종형 JK FF

- 레이스 현상 문제 해결. 하강엣지에서 동작함!

- 비동기 입력 : 클럭펄스와 관계없이 변화시킬 수 있는 입력

- 여기표 : 이러한 현재상태에서 저러한 다음상태로 가려면 입력엔 뭘 넣어야 하나?

레지스터

FF를 n개 모은 n비트 저장소! CP클록펄스가 공통으로 들어감

- 4비트 병렬 레지스터 : 공통 클럭 신호의 상승엣지에서 입력4개가 D FF 4개에 동시저장

- 시프트 레지스터 : CP가 있을 때마다 입력데이터가 한 비트씩 옆으로 옮겨가며 저장

- 카운터 : CP에 따라 수를 셈

- 동기식 : CP에 동기화되어 FF가 동시 동작

- 비동기식(리플 카운터) : 다른 FF의 출력을 CP로 사용함. 각 FF는 CP의 하강엣지에서 변함.

5. 집적 회로

칩. Integrated Circuit. IC.

컴퓨터 3세대 → IC등장

4세대 → VLSI 초대규모직접회로 등장

직접회로의 발전으로

- 소비 전력 감소

- 고속화 신뢰도 저렴화 경량화

반응형

'뚝딱 공부 상자 > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] Chapter6. 기억장치 (0) | 2022.06.25 |

|---|---|

| [컴퓨터 구조] Chapter5. 제어 장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 04. 중앙 처리 장치 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 02. 데이터의 표현 (0) | 2022.06.25 |

| [컴퓨터 구조] Chapter 01. 서론 (0) | 2022.06.25 |